# ALTAIR 88-DIAGNOSTIC CARD USER'S GUIDE

©MITS, Inc., 1977 First Printing, August, 1977

a subsidiary of **Pertec Computer Corporation**2450 Alamo S.E. /Albuquerque, New Mexico 87106

-

### TABLE OF CONTENTS

| Sec  | tion                                            | age  |

|------|-------------------------------------------------|------|

| 1.   | Introduction                                    |      |

|      | 1-1. Description                                | 3    |

|      | 1-2. Scope and Arrangement                      | 3    |

| 2.   | Theory of Operation                             |      |

|      | 2-1. General Contents                           | 7    |

|      | 2-2. Power Supply                               | 10   |

|      | 2-3. Digital Voltmeter                          | 10   |

|      | 2-4. Multiplexed Oscilloscope Display Circuit   | 11   |

|      | 2-5. Octal Display Circuit                      | 12   |

| 3.   | System Integration                              |      |

|      | 3-1. Normal Mode of Operation With Oscilloscope | 17   |

|      | 3-2. External Input Mode of Operation With      |      |

|      | Oscilloscope                                    | 17   |

|      |                                                 |      |

|      | LIST OF ILLUSTRATIONS                           |      |

| Num  | <u> </u>                                        | ge   |

| 2-1  | . 88-DC Schematic (sheet 1) ) En                | d of |

| 2-2  | . 88-DC Schematic (sheet 2)                     | eory |

| 2-3  | -3. 303 <sub>8</sub> Oscilloscope Display       |      |

| 3-1  | . Normal Mode of Operation With Oscilloscope    | 17   |

| 3-2  | . External Input Mode of Operation With         |      |

|      | Oscilloscope                                    | 18   |

|      |                                                 |      |

|      | LIST OF TABLES                                  |      |

| Numi | <u>Pa</u>                                       | ge   |

| 2-A. | . Symbol Definitions                            | 8    |

|      |                                                 |      |

88-DC September, 1977 -.

# SECTION I 88-DC INTRODUCTION

88-DC September, 1977

1/(2 Blank)

J

#### 1. INTRODUCTION

#### 1-1. <u>Description</u>

The Altair<sup>TM</sup> 88-DC Diagnostic Card provides a precise, effective method of troubleshooting for the Altair 8800 computer. The card offers three main functions using the following devices:

- An Eight-Bit-to-Octal Decoder/Display that allows the user to examine the data on any of the lines on the Altair bus;

- A Digital Voltmeter, switch-selectable between bus (+8v, +18v, -18v) and External Input (+9.99v full scale range) that can be used to measure the on-card regulator voltages;

- 3) An Output Jack for oscilloscope display referencing of data and control signals. The Synchronization is selectable from the Data Out and Data In lines and 16 control signals to provide a stable oscilloscope display.

Any combination of data, address and control lines can be selected (except where redundancy of DIP switches causes the computer to become inoperative--see Paragraph 2-3) to display up to eight signals on a single channel oscilloscope.

Troubleshooting of individual boards with critical timing relationships is possible through the 10-pin right angle connector which acts as an external input. (Assembly of a special user-supplied cable is required to meet individual needs.)

#### 1-2. Scope and Arrangement

The 88-DC User's Guide is divided into two main parts:

- a brief theory of operation section, complete with schematics, designed to give the user a basic understanding of the card's circuit operation;

- 2) directions for system integration.

88-DC September, 1977

3/(4 Blank)

SECTION II 88-DG THEORY OF OPERATION

88-DC September, 1977

5/(6 Blank)

#### 2. THEORY OF OPERATION

### 2-1. <u>General Contents</u>

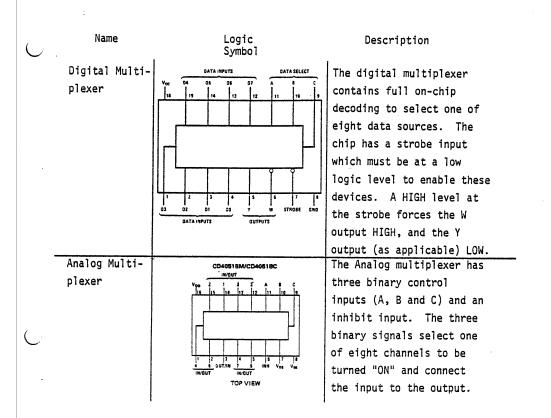

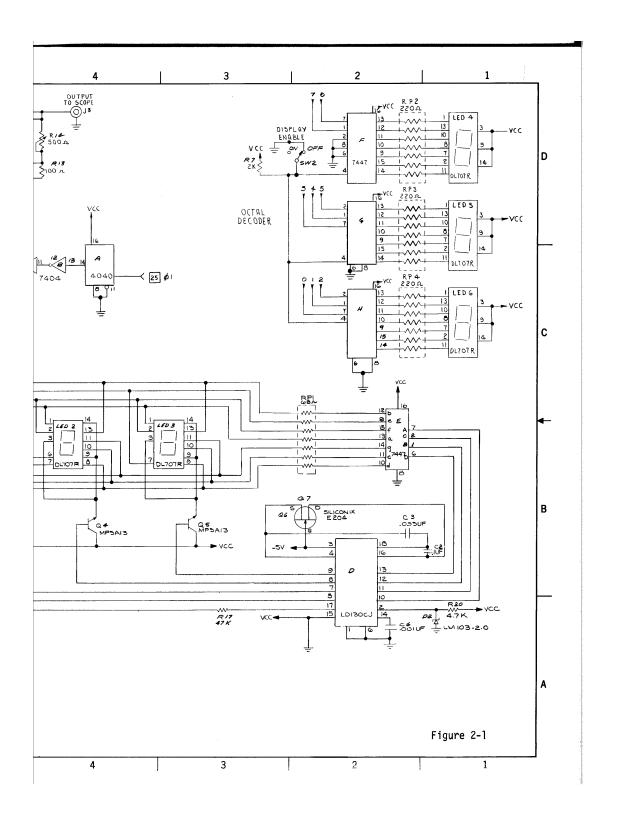

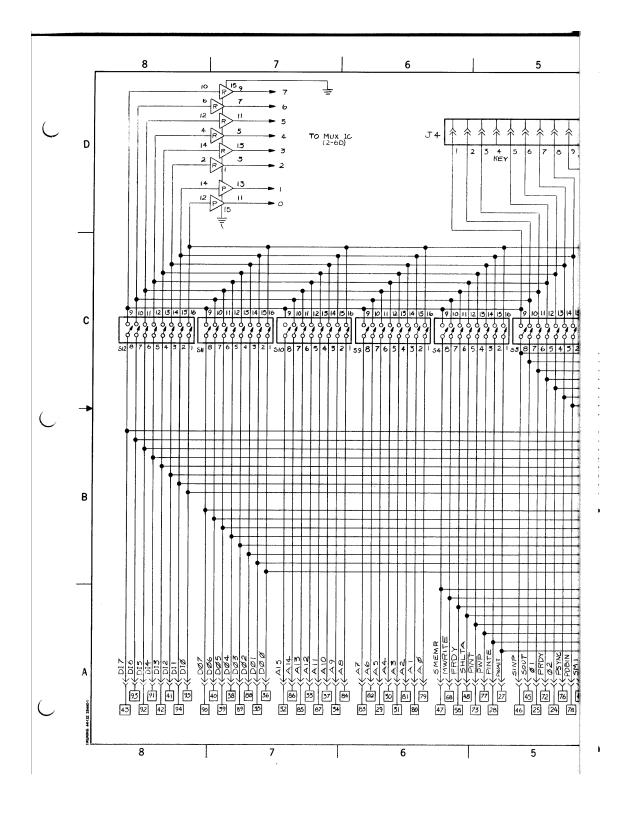

Section II contains a description of the circuitry operation of the 88-DC card, with references to the schematics, Figures 2-1 and 2-2. The logic symbols used in these figures are explained in Table 2-A, which presents the functional name, symbolic representation and a brief description of each logic circuit.

The active state of the inputs and outputs of the circuits is graphically displayed by the presence or absence of small circles. A circle at the <u>input</u> of a circuit indicates that the input is an active LOW; i.e. a LOW signal will enable the input. A circle at the <u>output</u> of a circuit indicates that the output is an active LOW; i.e. the output is LOW in the actuated state. Conversely, the absence of a circle indicates that the input or output is active HIGH.

88-DC September, 1977

| Table 2-A. Symbol Definitions                  |                                                                                                        |                                                                                                                                                                                 |  |  |  |  |  |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Name                                           | Logic<br>Symbol                                                                                        | Description                                                                                                                                                                     |  |  |  |  |  |  |  |

| NAND gate                                      | ₩ To Y                                                                                                 | The NAND gate performs one of the fundamental logic functions. All of the inputs have to be enabled (HIGH) to produce the desired (LOW) output. The                             |  |  |  |  |  |  |  |

|                                                | Y = <del>AB</del> N                                                                                    | output is HIGH if any of the inputs are LOW.                                                                                                                                    |  |  |  |  |  |  |  |

| Inverter                                       | A—————————————————————————————————————                                                                 | The inverter is a device whose output is the opposite state of the input.                                                                                                       |  |  |  |  |  |  |  |

| Non-Inverting<br>Bus Driver                    | A A                                                                                                    | The non-inverting bus driver is a device whose output is the same state as the input. Data is enabled through the device by applying a (LOW) signal to the E input.             |  |  |  |  |  |  |  |

| Eight-Channel<br>Analog Multi-<br>plexer (MUX) | 11   10   A B C COM   -3   A 10 A 11 A 12 A 13 A 14 A 15 A 16 A 17   13   14   15   12   1   5   2   4 | This eight-channel multi- plexer has three binary control inputs (A, B and C) which select one of eight channels (AIO-AI7) to be turned on and con- nected to the output (COM). |  |  |  |  |  |  |  |

#### 2-2. Power Supply (Figure 2-1)

The +5v regulated DC voltage, which supplies Vcc for most of the ICs, is provided by a 3 amp voltage regulator, VRI (zone D7). Current is input to VRI from pins 1 and 51 (the unregulated +8v bus).

The -5v regulated DC voltage is supplied to IC D (zone B2) from regulator Q1 (zone D8). IC D draws approximately 3mA of current. 2-3. Digital Voltmeter (Figure 2-1)

The DVM section of the card allows voltages to be tested and numerically displayed on LEDs 1, 2 and 3 (zones B5 through B3). Voltage levels are converted to a 3-digit number by means of a CMOS A/D Converter, IC D (zone B2). IC D utilizes the "quantized feedback" conversion technique which provides auto-zero and auto-polarity functions to eliminate the need for additional external circuitry. The auto-zero feature also regulates drift automatically. The circuit is made functionally complete by the addition of  $\mathrm{C}_{\mathrm{AZ}}$  (C2),  $\mathrm{C}_{\mathrm{INT}}$  (C3),  $\mathrm{C}_{\mathrm{OSC}}$  (C6),  $\mathrm{V}_{\mathrm{REF}}$  (D2) and  $\pm 5$  volt supplies (VR1 and Q1).

Switch S1 has four switch selectable inputs (+8v,  $\pm 18v$  and EXT) which are calibrated by the adjustment of the corresponding trim pots: R1 for +8v, R2 for +18v, R3 for -18v and R4 for EXT. The Binary Coded Decimal (BCD) output of IC D is sent to IC E (zone B2) which is a BCD-to-7-segment decoder. The output then goes through resistor pack RP1 which contains seven 68 ohm resistors, and to the anodes (A-G) of the LED displays.

The Digit Strobe outputs of IC D (pins 7, 8 and 9) are switched by Q3, Q4 and Q5 (zones B4, B4 and B3, respectively). The "Sign/Over-Range" output (indicating polarity or excessive voltage) on pin 5 goes to Q2 (zone B6). D1 is turned on if it receives a positive input from Q2 and off if a negative input is received. D1 and LEDs 1, 2 and 3 flash in an over-range condition.

The reference voltage ( $V_{REF}$ ) to pin 2 of IC D is furnished by D2 (zone A1), a 2v zener diode. C2, the auto-zero capacitor ( $C_{AZ}$ ) has an optimum value of .lmf over the full sampling range. C3, the integrator capacitor ( $C_{INT}$ ) and C6, the oscillator capacitor ( $C_{OSC}$ ) determine the sampling rate (approximately 5 samples/second). The  $C_{OSC}$  frequency is approximately 30KHz.

The input impedance of IC D is >1000 megohms. Power consumption s 25 milliwatts, typical, and the accuracy is better than 1%. The External Input range of the digital voltmeter is  $\pm 9.99v$  with 10mv resolution. Resolution on the  $\pm 8v$  position is also 10mv, and resolution on the  $\pm 18v$  positions is 100mv. Decimal point placing is determined by S1 (zone A6).

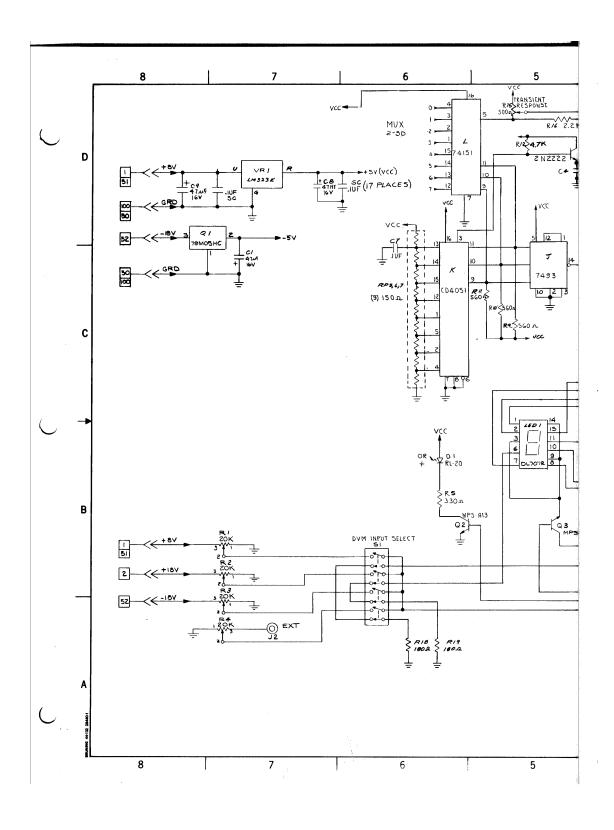

# 2-4. Multiplexed Oscilloscope Display Circuit (Figure 2-2)

Timing relationships between several signals can be visually checked with the Multiplexed Oscilloscope Display Circuit. Eight signals, selected by a combination of S3, S4 (16 control lines, zones C5 and C6); S9, S10 (AØ-A16, zones C6 and C7); S11 (D01-D07, zone C7); and C12 (DIØ-DI7, zone C8), can be displayed on a single channel of an oscilloscope. Oscilloscope sync is switch selectable from S5, S6 (16 control signals, zone B2), S7 (DOØ-DO7, zone B3), and S8 (DIØ-DI7, zone B3).

The display on the oscilloscope coincides with the silkscreening under the switches. For example:

If the DOØ-DO7 lines are selected for display, they are shown in numerical order (from top to bottom) on the CRT.

If PWAIT, PDBIN, PSYNC,  $\emptyset$ 2, PRDY,  $\emptyset$ 1, MWRITE and SMEMR are selected for display, they appear in the same order on the CRT (from top to bottom).

#### NOTE

Redundancy of switch selection will cause the computer to become inoperative. For example, if the #2 position of switch S3 (PDBIN) is selected, the #2 position of the other nine switches cannot be selected at the same time.

The display operation is accomplished by applying the eight selected signals to the digital MUX, IC L (zone D6). The MUX Select Inputs (pins 9, 10 and 11 of ICs L and K, zones D6 and C6) are incremented by the 3-bit output from IC J (zone C5) which receives an input frequency of 1953Hz from IC A (zone C4). This frequency is derived through divider IC A (zone C4) from Ø1 of the system clock.

8-DC eptember, 1977 The 3-bit output of IC J causes IC L to select one of its eight applied signals and increment by one on each count. IC K is simultaneously incremented in the same manner and selects one of eight DC voltage levels. The digital output of IC L (pins 9, 10 and 11, zone D5) and the DC level output of IC K (pins 9, 10 and 11, zone C6) are summed, providing a different DC reference level for each trace and vertically separating the traces from each other on the oscilloscope screen.

The DC level output of IC K goes through Q6 (zone B3) and R14 (zone D4) to the summing point. R14 adjusts the magnitude of DC offset which varies trace separation. The scope's Variable Vertical Sensitivity Control may be used to adjust the overall display amplitude. The hex inverter, IC B (zone C4), is used for signal shaping and inversion where necessary.

The External Sync for the oscilloscope is provided by selecting the desired signal(s) from S5, S6 (16 control signals, zone B2), S7 (DOD-DO7, zone B3) or S8 (DID-DI7, zone B3). For example, Sync selection can be used to select a pulse (e.g. the system clock) or a combination of pulses (e.g. an octal word) to reference the signal display. The selected sync signals go to IC C (an 8-input NAND gate, zone A3), then to the BNC connector.

#### 2-5. Octal Display Circuit (Figures 2-1, 2-2 and 2-3)

The Octal Display Circuit provides a simple method for checking short programs by displaying the information being transmitted on the data bus on LEDs 3, 4 and 5. The circuit is switch selectable between the DO and DI lines via section 1 of switch S2 (Figure 2-2, zone D2).

NOTE

When used with the 8800a computer, the circuit can monitor only the DO lines.

LED #4 is connected to IC F (Figure 2-1, zone D2) and displays the numbers 0, 1 and 2 only. LEDs #5 and #6 are connected to ICs G and H, respectively, and display the numbers 0 through 7 (the largest octal number being 377). ICs F, G and H are BCD-to-7-segment decoders. Outputs A through G are sent through resistor packs RPl through RP4 which each contain seven 220 ohm resistors. The signals are then sent to the anodes of the 7-segment displays of LEDs 3, 4 and 5.

In order to conserve power when the circuit is not in use, section 2 of switch S2 disables display decoder ICs F, G and H.

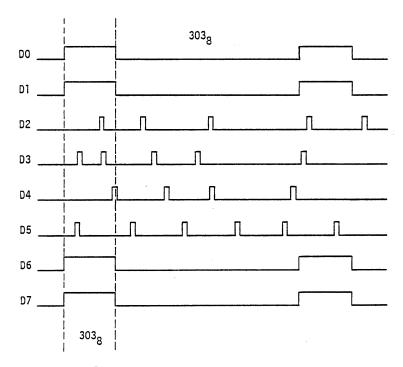

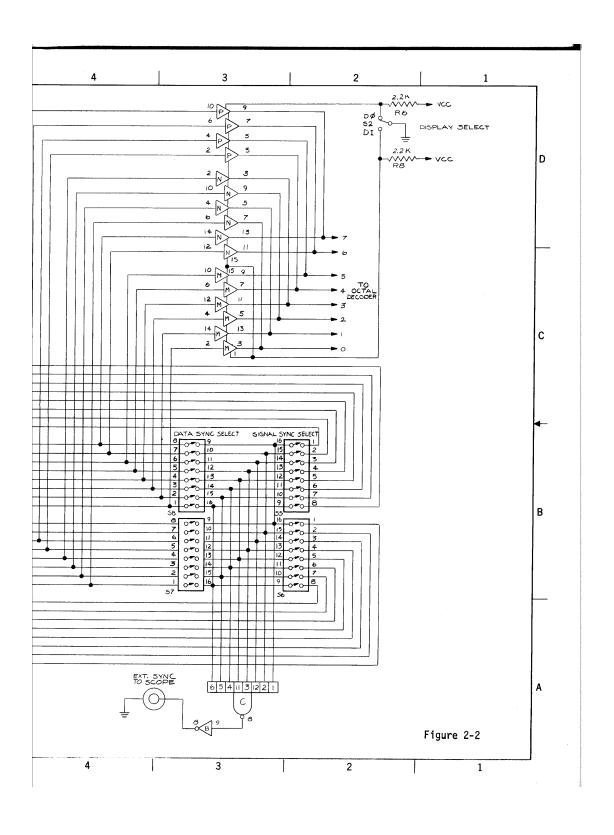

Figure 2-3 is an example of a scope display showing  $303_8$ . Note that DØ, D1, D6 and D7 are HIGH. The narrow lines are switching pulses that may be disregarded.

Figure 2-3. 303<sub>8</sub> Oscilloscope Display

88-DC September, 1977

13/(14 Blank)

•

SECTION III 88-DC SYSTEM INTEGRATION

88-DC September, 1977

15/(16 Blank)

#### 3. SYSTEM INTEGRATION

## 3-1. Normal Mode of Operation With Oscilloscope (Figure 3-1)

To connect the sync output, attach one end of a BNC-BNC cable to the "sync output" socket on the 88-DC card and the other end to the "external sync" socket on the oscilloscope.

To connect the data output, attach one end of a BNC-BNC cable to the "data output" socket on the 88-DC card and the other end to the "vertical amplifier" socket on the oscilloscope.

# 3-2. External Input Mode of Operation With Oscilloscope (Figure 3-2)

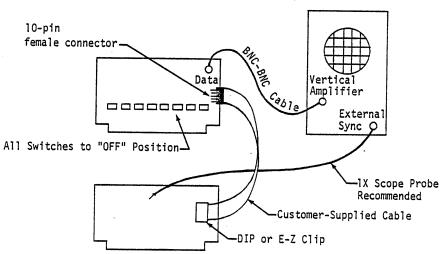

To use the external input portion of the board, the user must construct a special cable. One end of the cable must have a 10-pin female socket to plug into the 10-pin male connector on the 88-DC card. The other end (which connects to the problem board) may have "E-Z clips" or "DIP clips" for termination. Sync is selected from the desired signals by means of an oscilloscope probe. A BNC-BNC cable should also be used to connect the 88-DC card's "data output" socket to the oscilloscope's "vertical amplifier" socket. All of the 88-DC card's switches should be turned off while testing in this mode.

Sync Data

Vertical Amplifier

Externa.

Sync O.

BNC-BNC Cable

Figure 3-1. Normal Mode of Operation

Figure 3-2. External Input Mode of Operation