# ${\sf Helios}\ {\rm I\!I}$

Model 2 (Part No. 300000) Model 4 (Part No.304000)

# Disk Memory System Manual

#### Processor Technology Corporation

7100 Johnson Industrial Drive Pleasanton, CA 94566 Telephone (415) 829-2600

Copyright (C) 1978, Processor Technology Corporation Second Printing, March, 1978 Literature Kit No. 730009 All rights reserved.

#### PREFACE

As a convenience feature for the user, this three-ring binder is an "easel" binder. The cover is hinged across the front and back as well as down the binding. You may find it helpful to stand up the binder in its easel position for two-handed operations when reference to the manual is necessary at the same time, as in the assembly sections, or troubleshooting.

TO USE THIS FEATURE: (Refer to illustration below)

- 1. Lay the manual open on a table. Bend back the full width of the bottom half of the binder along the creased hinge until a resistance to further bending is felt.

- Set the manual up on the table, with the bottom of the pages down against the table, and the top inclining away from you. (It is supported from falling by the portion of the binder you have bent back.)

IMPORTANT NOTE

The first part of this manual you should read is at the very end: the Updates section. Integrate this information into your manual before you begin.

The reader is invited to participate in the evolution of this manual. Please send your comments or suggestions for improvements to Processor Technology.

#### In Memoriam

This book is dedicated in grateful memory of Noel Leffler, a fine engineer and good person who is largely responsible for this book, but who died before his Helios II project was completed.

# This Document was scanned and contributed by:

# Barry A. Watzman

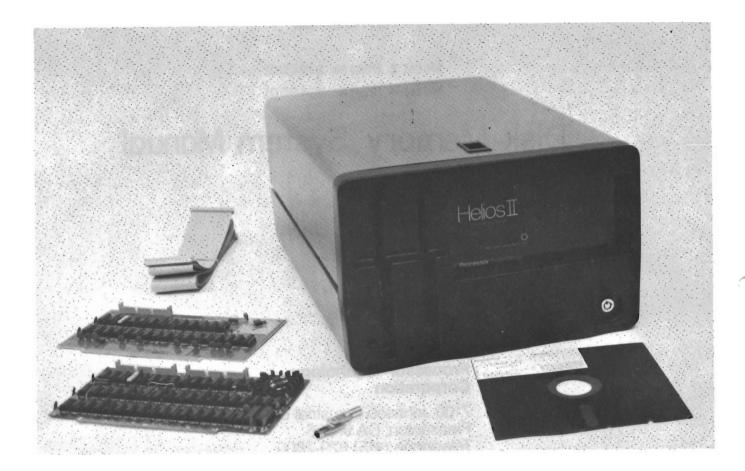

Fig. Ø Helios II System: Diskette Drive Cabinet, Controller and Formatter PCBs and Diskette containing PTDOS

Ĵ

#### CONTENTS OUTLINE

Detailed contents precede each section.

#### SECTION

- 1 INTRODUCTION

- 2 SPECIFICATIONS

- 3 ASSEMBLY AND TESTING

- 4 OPERATING INSTRUCTIONS

- 5 TESTING AND DIAGNOSTICS

- 6 MAINTENANCE

- 7 THEORY OF OPERATION

- 8 DRAWINGS

- 9 APPENDIX

- 10 UPDATES

SOFTWARE MANUAL: PTDOS User's Guide

NOTE

v

Parts of this manual relating to the diskette drive assembly are reprinted with permission of PerSci, Inc., 1212 Nebraska Ave., W. Los Angeles, CA 90025

## LIST OF FIGURES

| FIG. #                                             |                                                                                                                                                                                            | PAGE                         |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| F-Ø                                                | Frontispiece, Helios II System: Diskette<br>Drive Cabinet, Controller and Formatter PCBs,<br>and Diskette containing PTDOS (photo)                                                         | ii                           |

| F-iii                                              | Easel Binder (photo)                                                                                                                                                                       | iii                          |

| 1-1                                                | Helios II System, Generalized Block Diagram                                                                                                                                                | 1-1                          |

| 3-1<br>3-2<br>3-3<br>3-4                           | DIP Sockets                                                                                                                                                                                | 3-4<br>3-5                   |

| 3-5                                                | Diskette Drive DC Power and Signal Connectors (photo)                                                                                                                                      | 3-10                         |

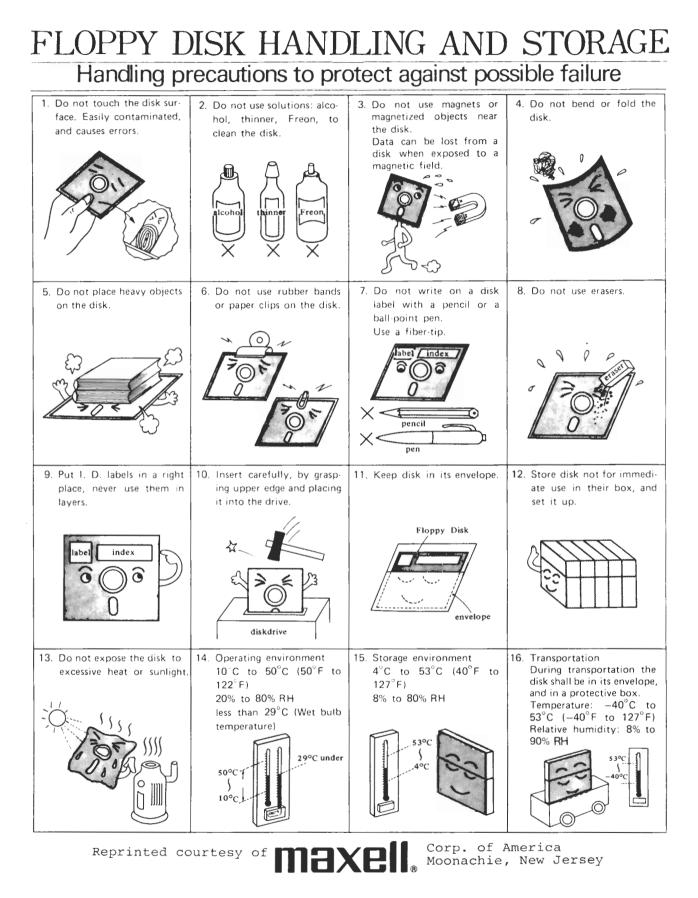

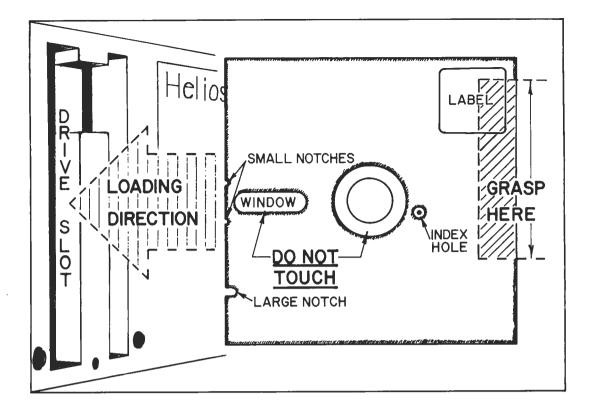

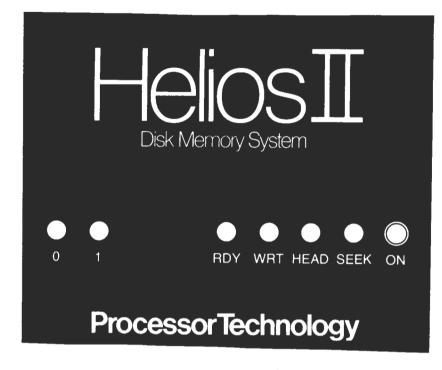

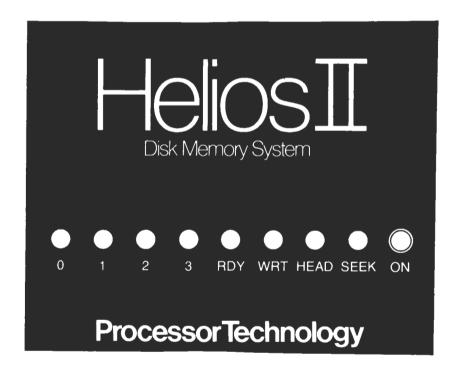

| 4 - 1<br>4 - 2<br>4 - 3<br>4 - 4<br>4 - 5<br>4 - 6 | Helios II Front Panel (photo)Helios System TerminologyFloppy Disk Handling and StorageDiskette Orientation for LoadingHelios II Indicator Panel, Model 2Helios II Indicator Panel, Model 4 | 4-2<br>4-5<br>4-7<br>4-12    |

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6             | Automatic Test Report Format, Printout                                                                                                                                                     | 5-30<br>5-31<br>5-36<br>5-38 |

| 6-1<br>6-2<br>6-3                                  | Positioner Tracks (Unit $\emptyset$ )                                                                                                                                                      | 6-6                          |

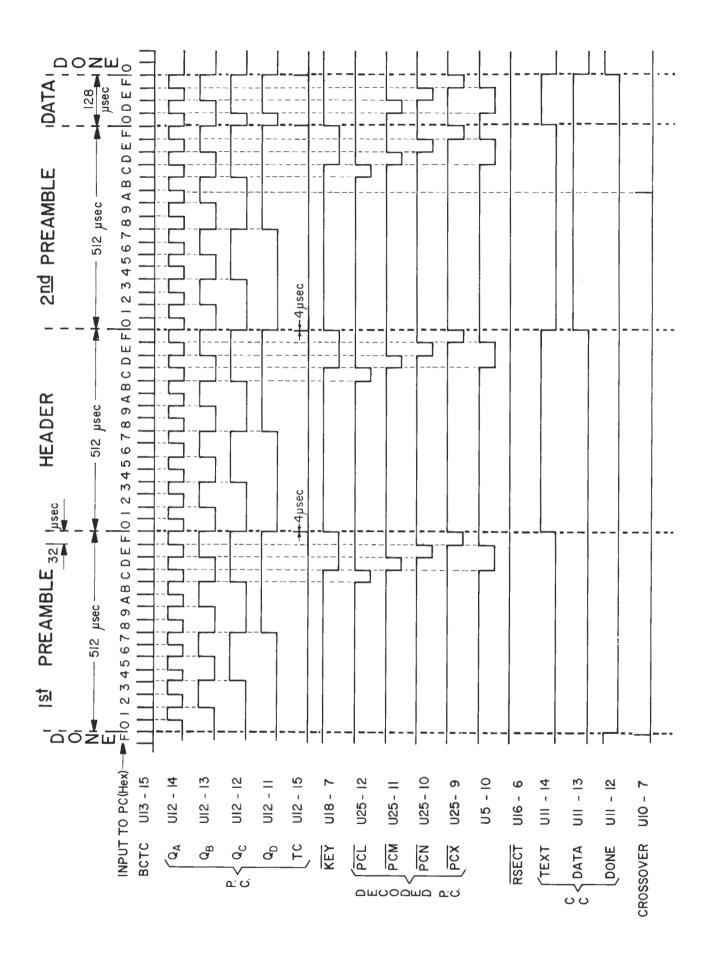

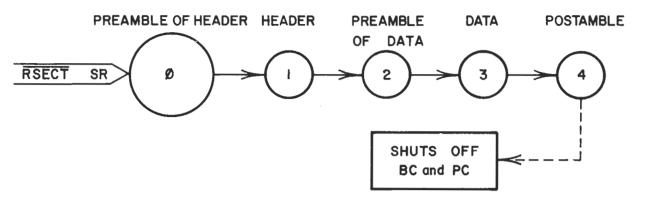

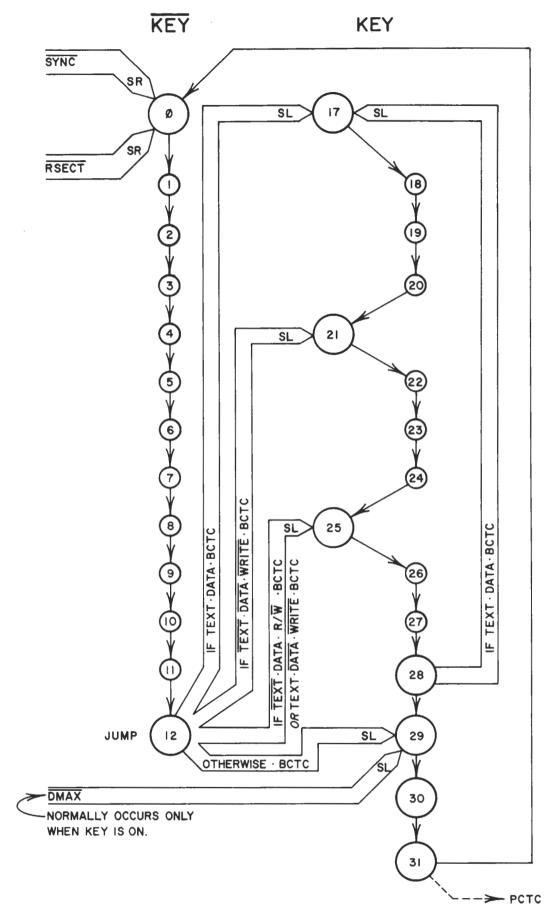

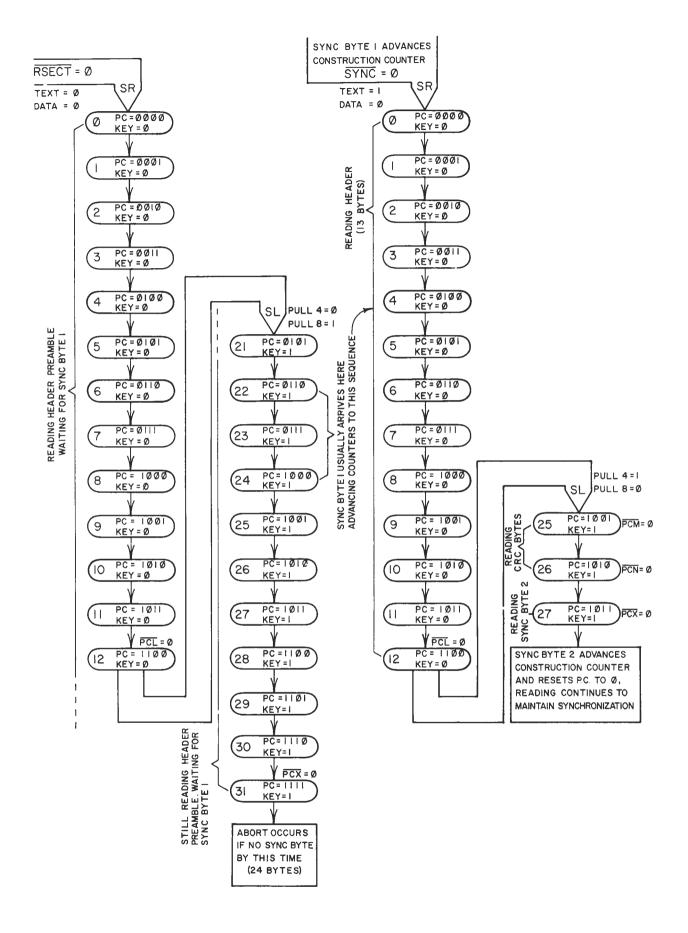

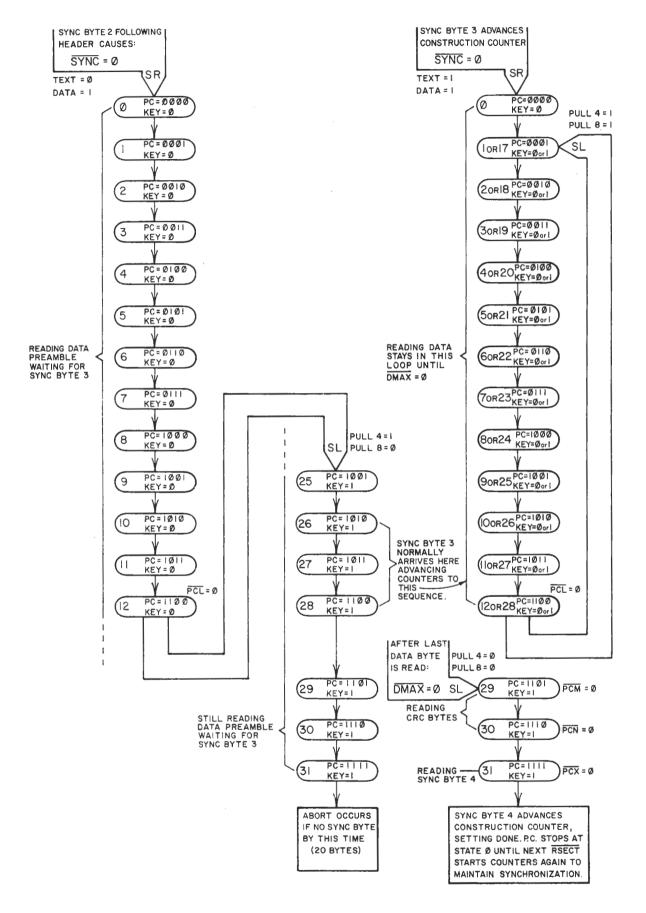

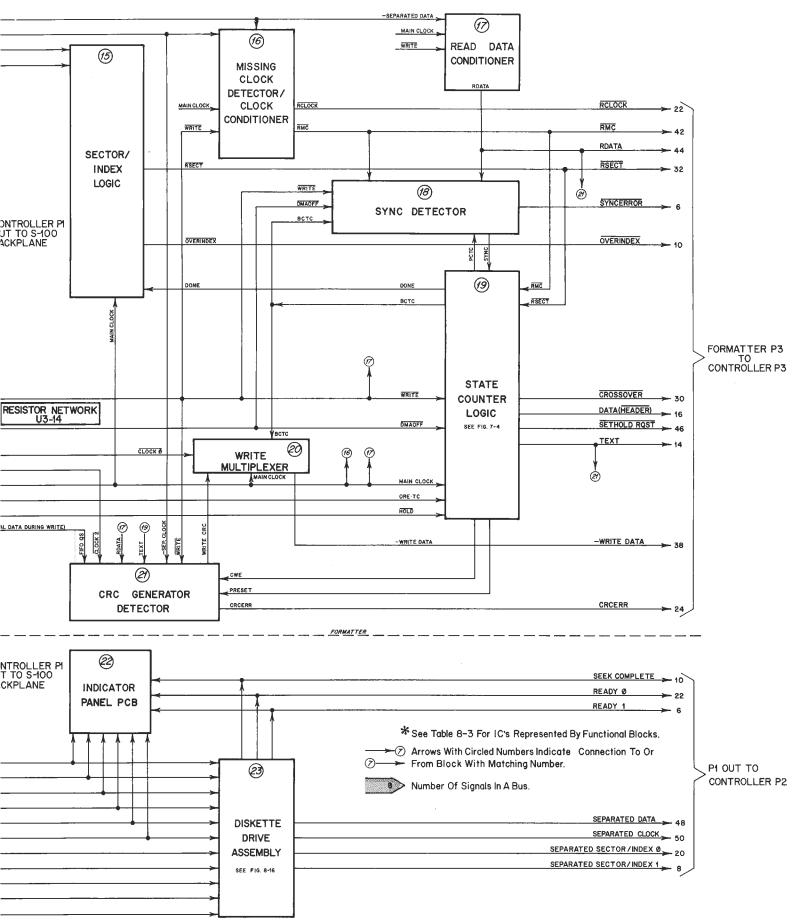

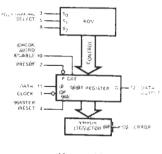

| 7-Ø<br>7-1<br>7-2<br>7-3<br>7-4<br>7-5A            | Controller/Formatter Simplified Block Diagram<br>Format within a Block                                                                                                                     | 7-7<br>7-7<br>7-7            |

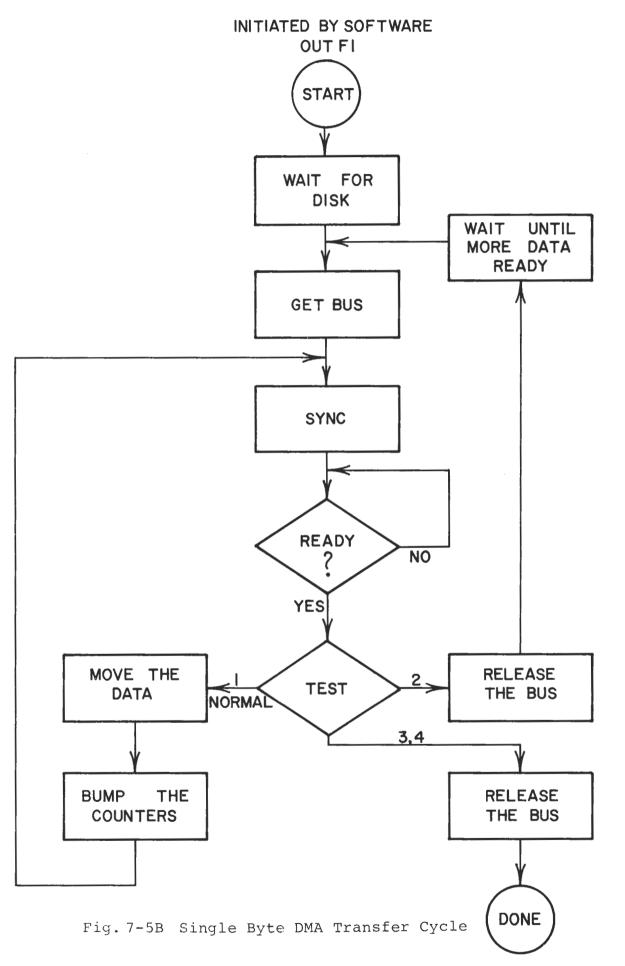

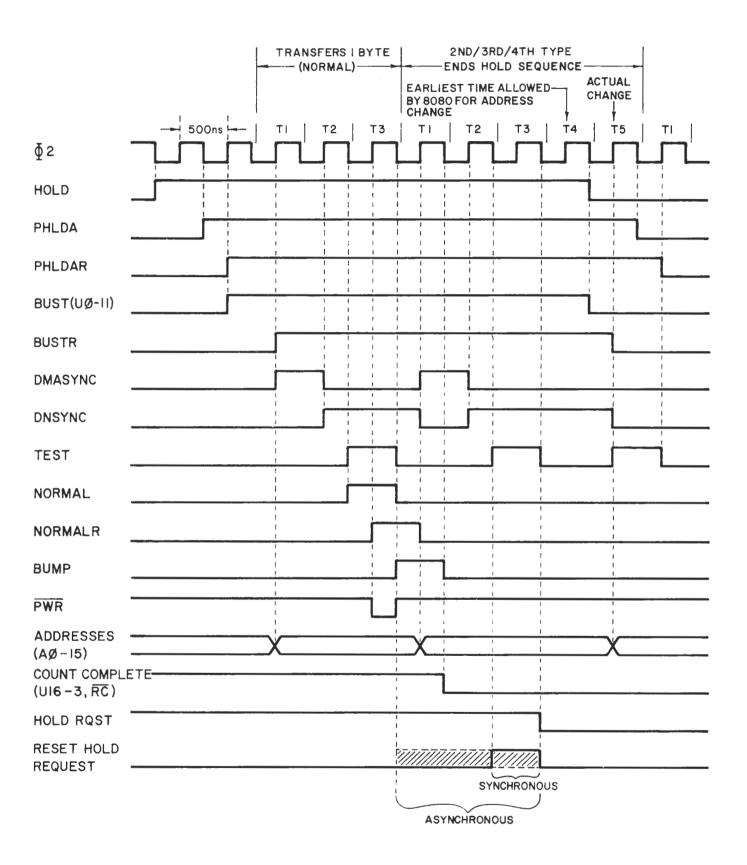

| 7-5B<br>7-6<br>7-7<br>7-8                          | the PTDOS (Flowchart)                                                                                                                                                                      | 7-28<br>7-30<br>7-49<br>7-50 |

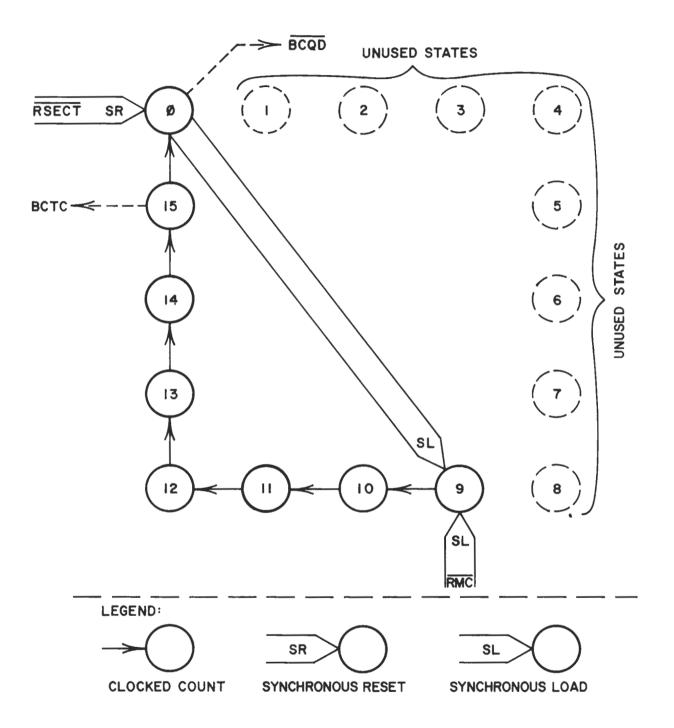

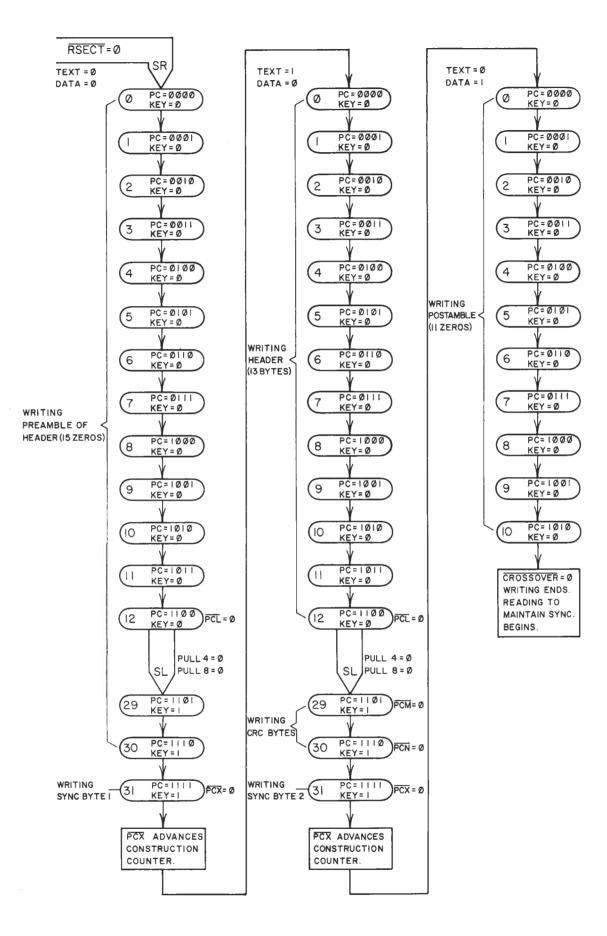

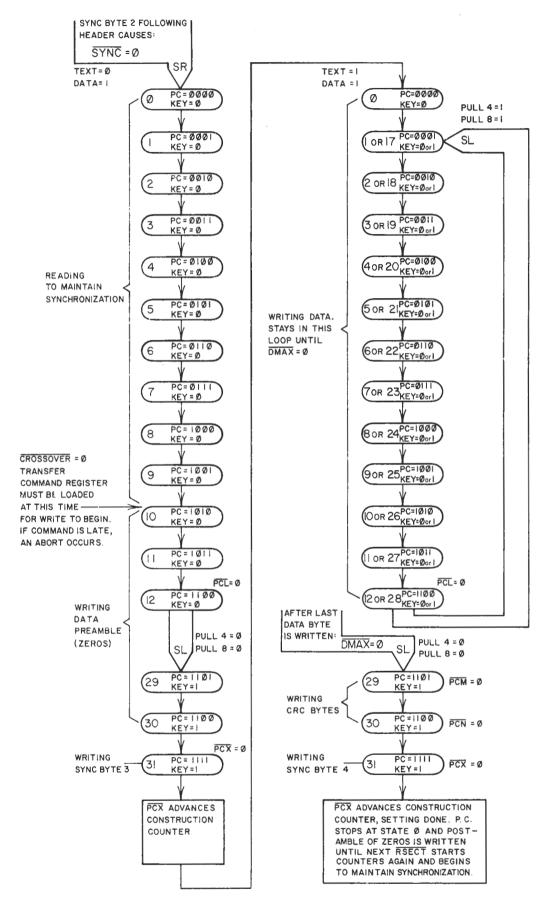

| 7-9                                                | PC and KEY Sequence, State Diagram                                                                                                                                                         | 7-51                         |

| 7-10<br>7-11                                       | State Counters During Read Header Command                                                                                                                                                  | 7-53<br>7-54                 |

| 7-12                                               | State Counters During Write Header Command                                                                                                                                                 | 7-55                         |

| 7-13                                               | State Counters During Write Data Command.                                                                                                                                                  | 7-56                         |

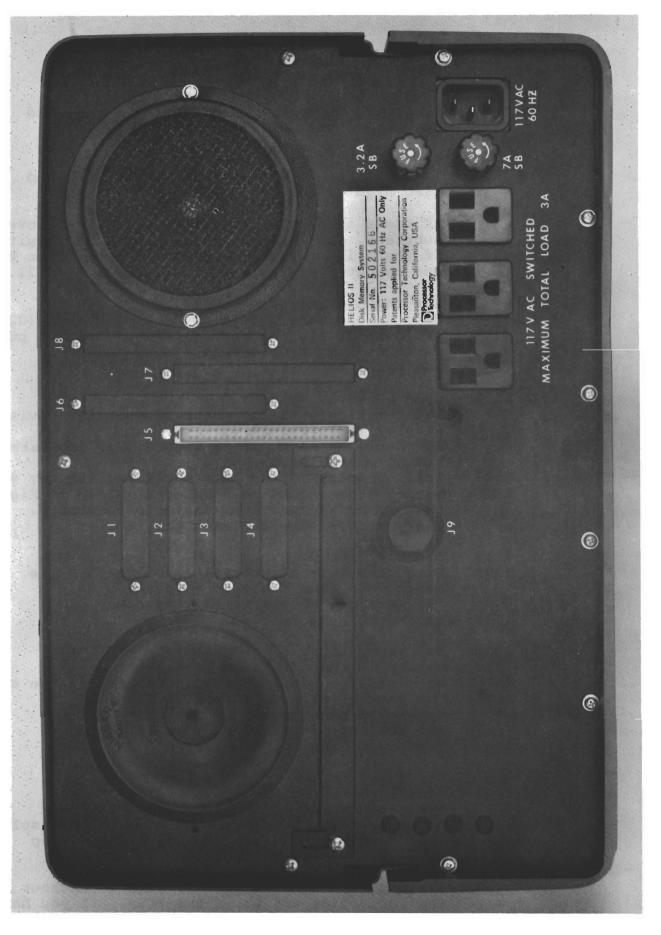

| 7-14                                               | Helios II Dual Diskette Drive Cabinet<br>(Model 2) (photo)                                                                                                                                 | 7-58                         |

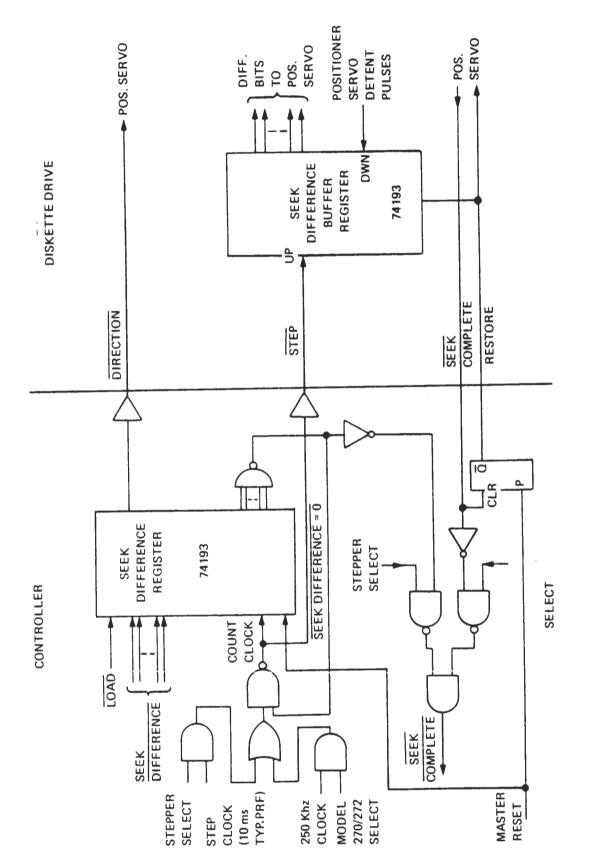

| 7-15                                               | Simplified Controller Design Configuration                                                                                                                                                 |                              |

| 7-16                                               | with Fast Multi-Track Seek and Restore                                                                                                                                                     | 7-61                         |

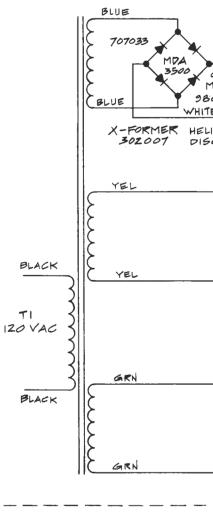

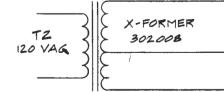

| •                                                  | Wiring Diagram                                                                                                                                                                             | 7-63                         |

vi

| FIG. #                                                      |                                                                                                            | FIG                                                         |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|                                                             | MODEL 2                                                                                                    |                                                             |

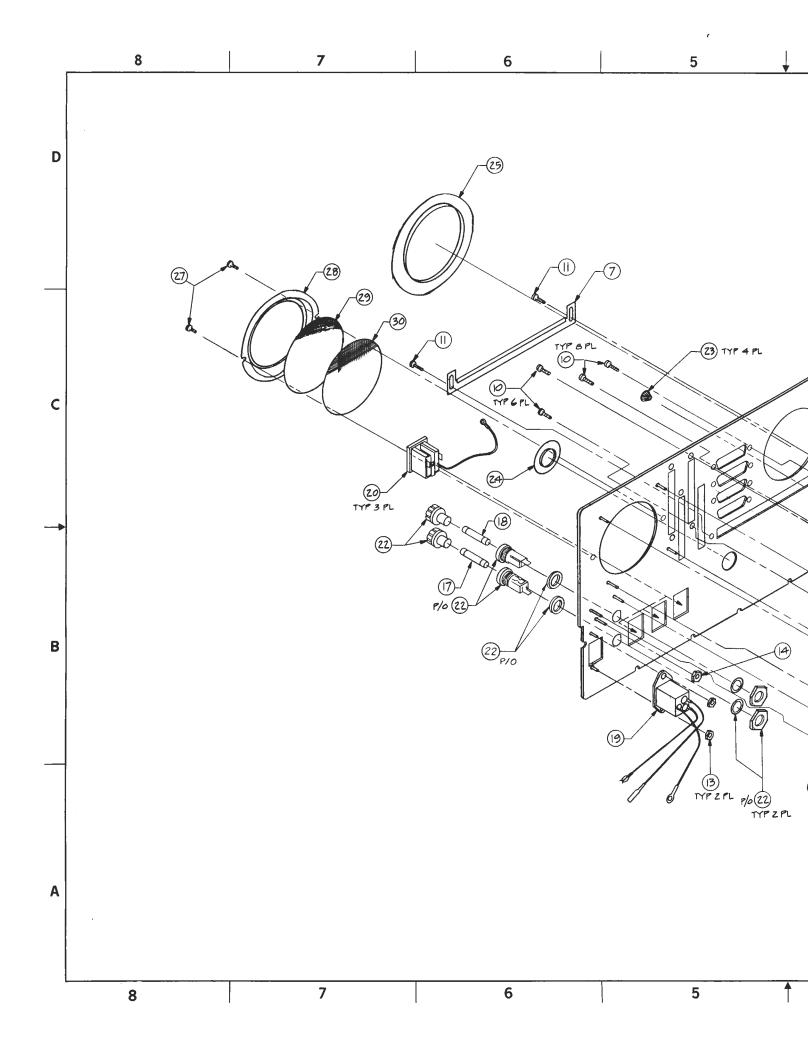

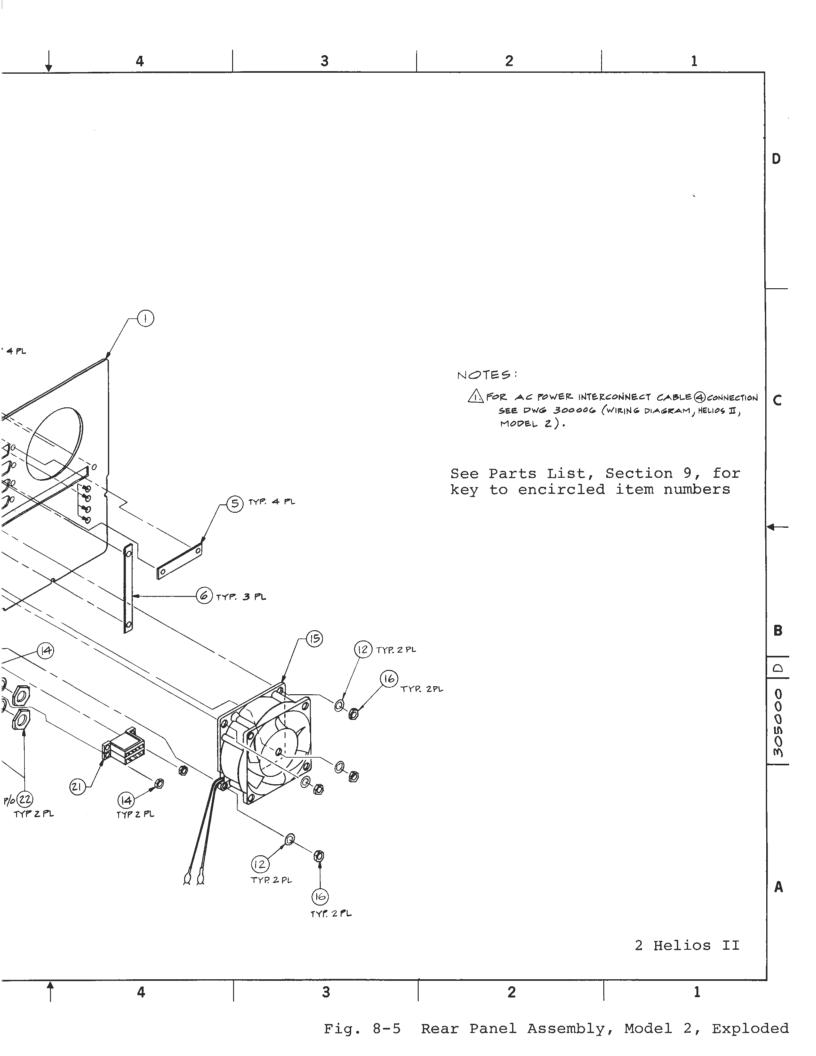

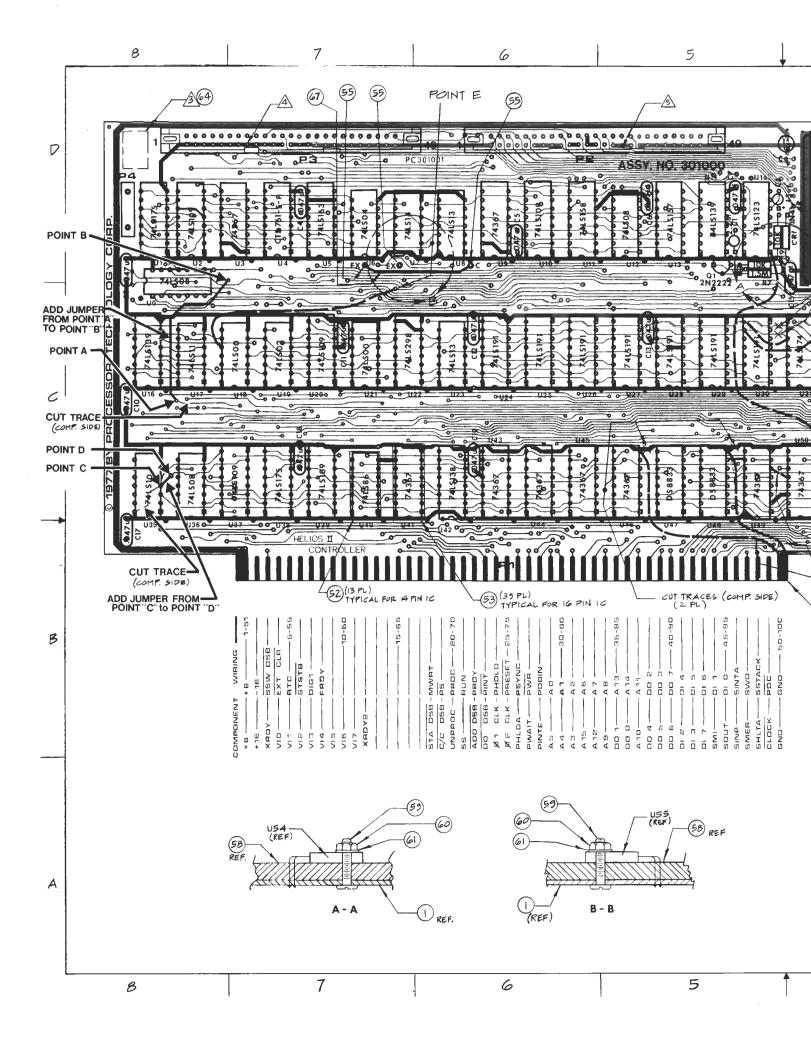

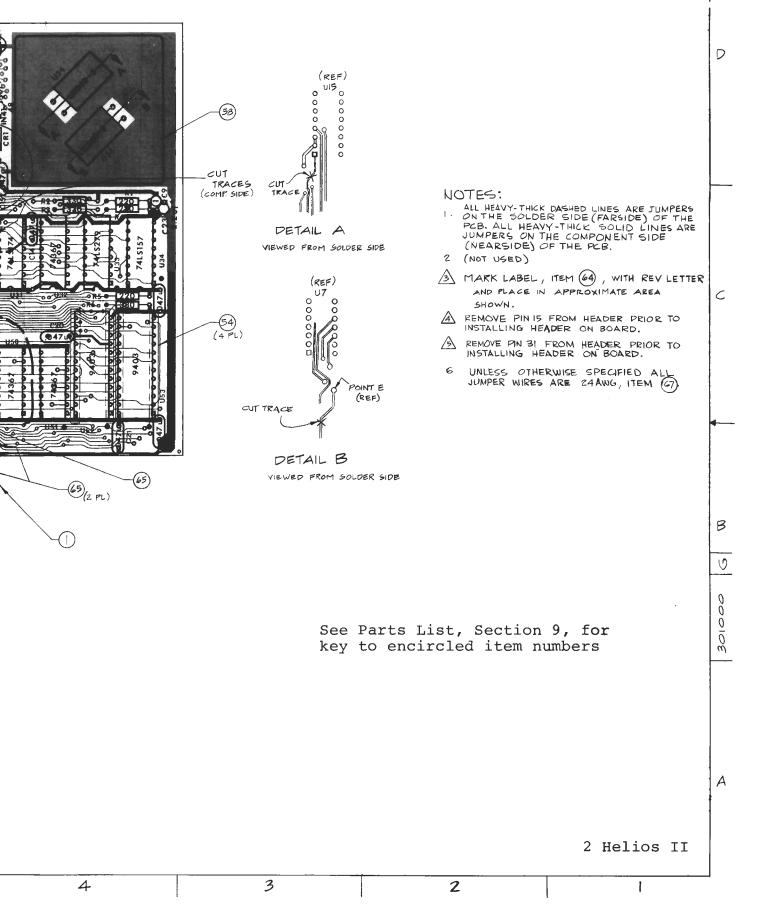

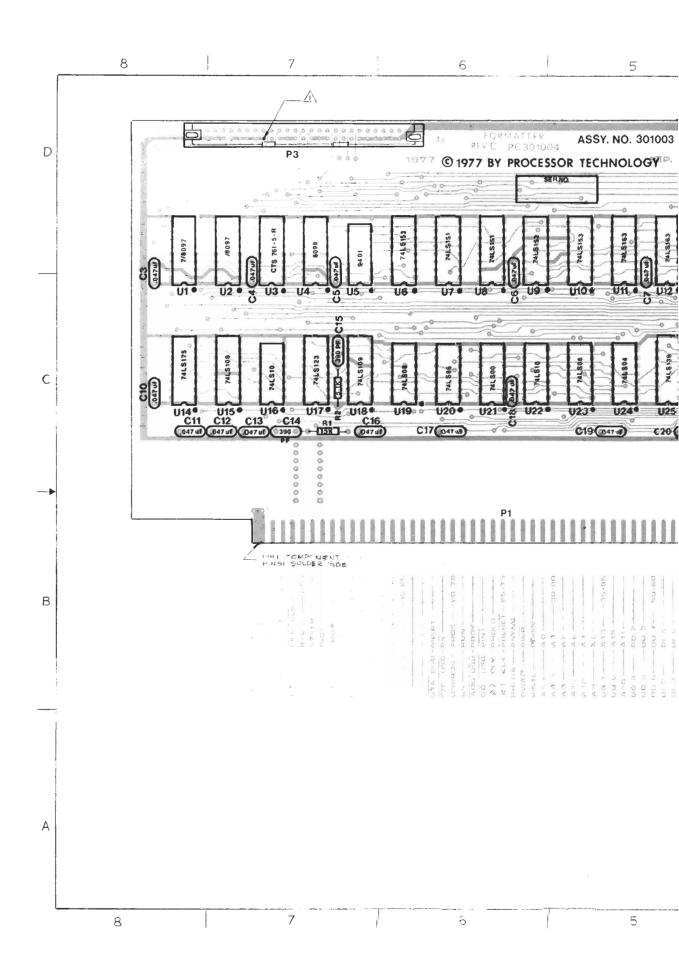

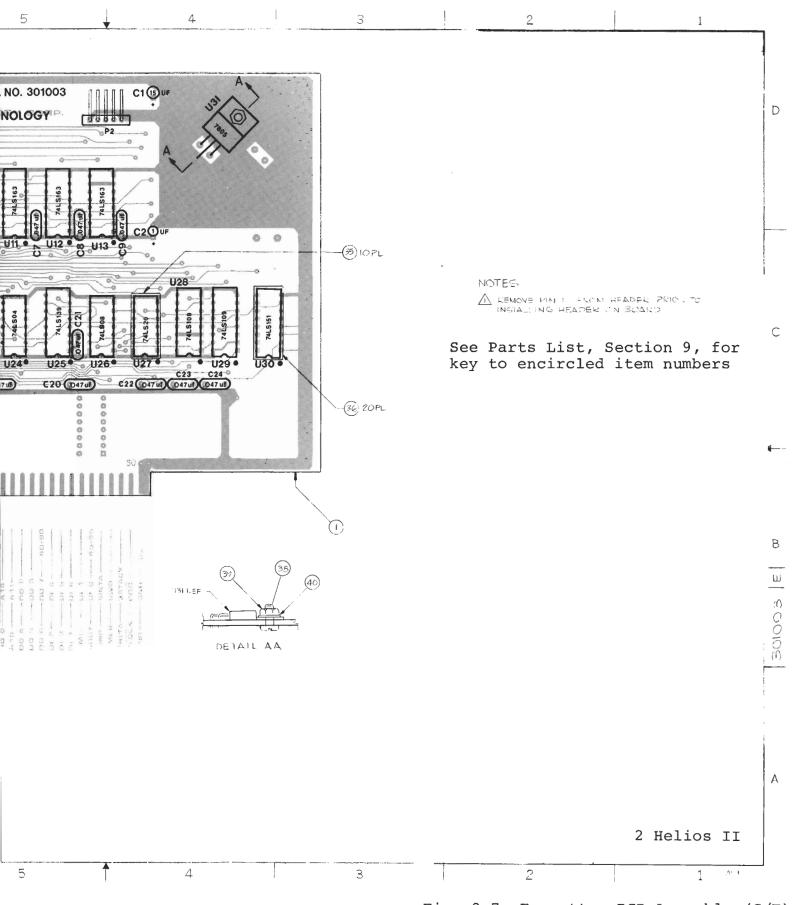

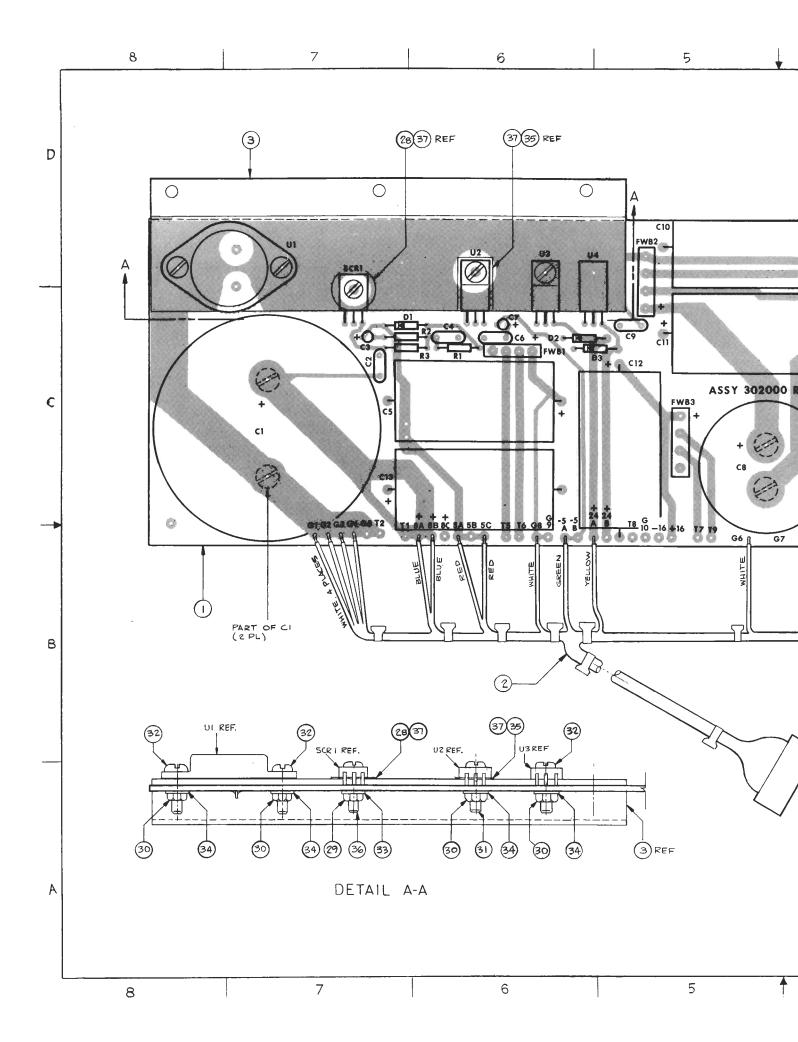

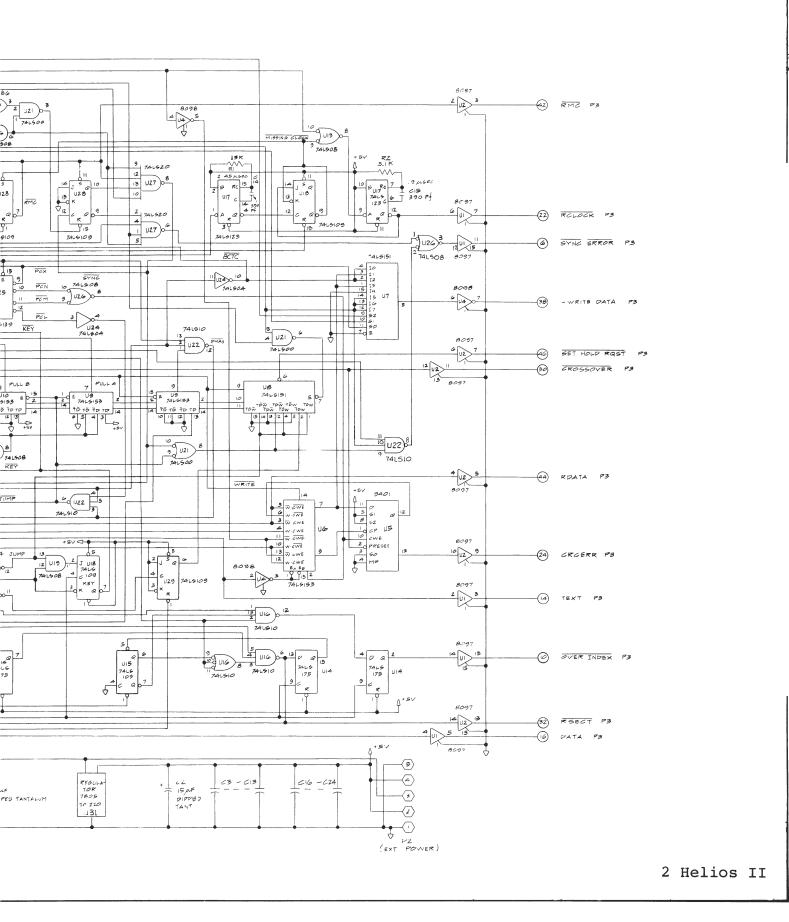

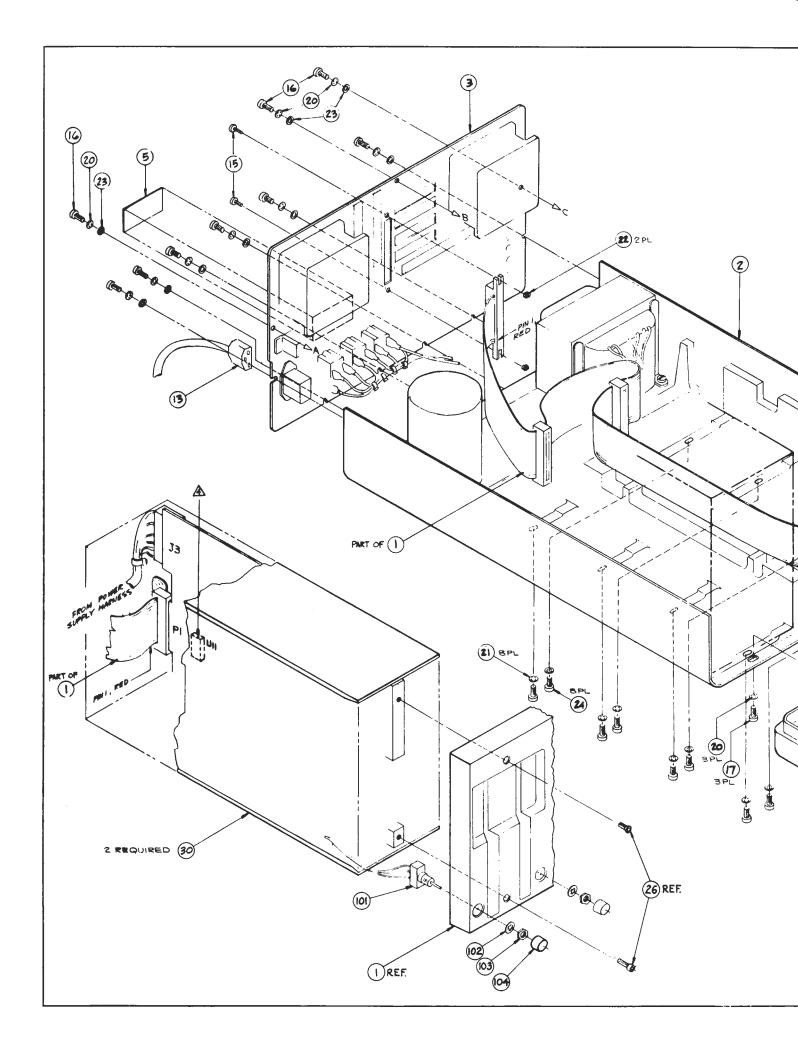

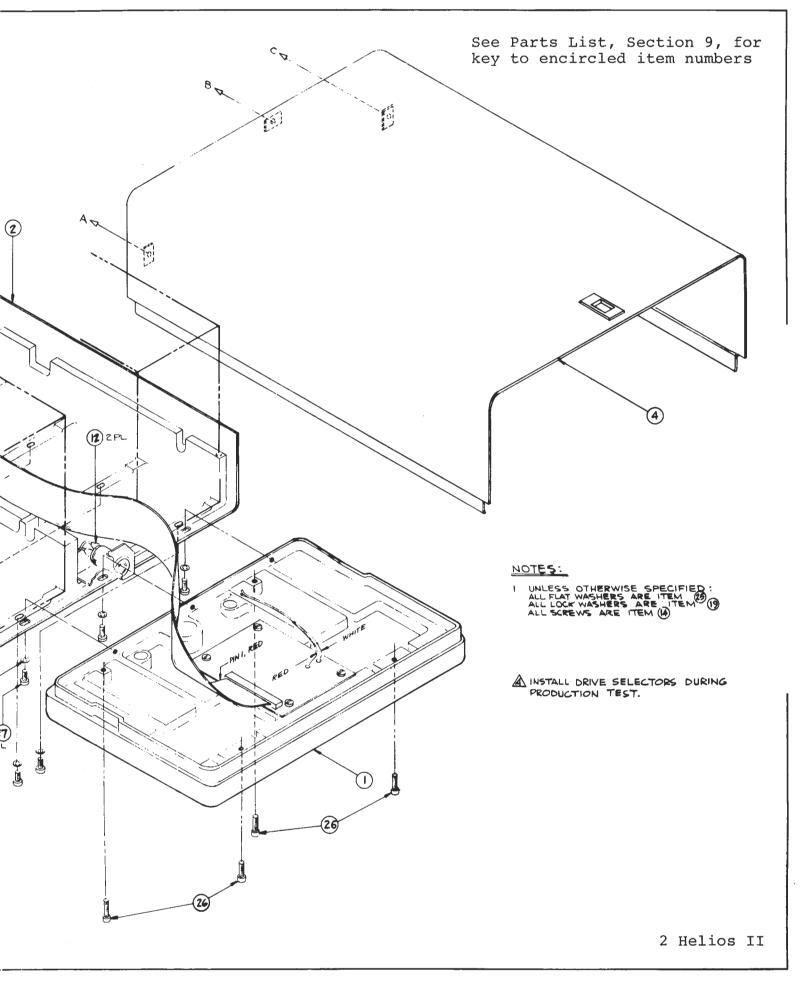

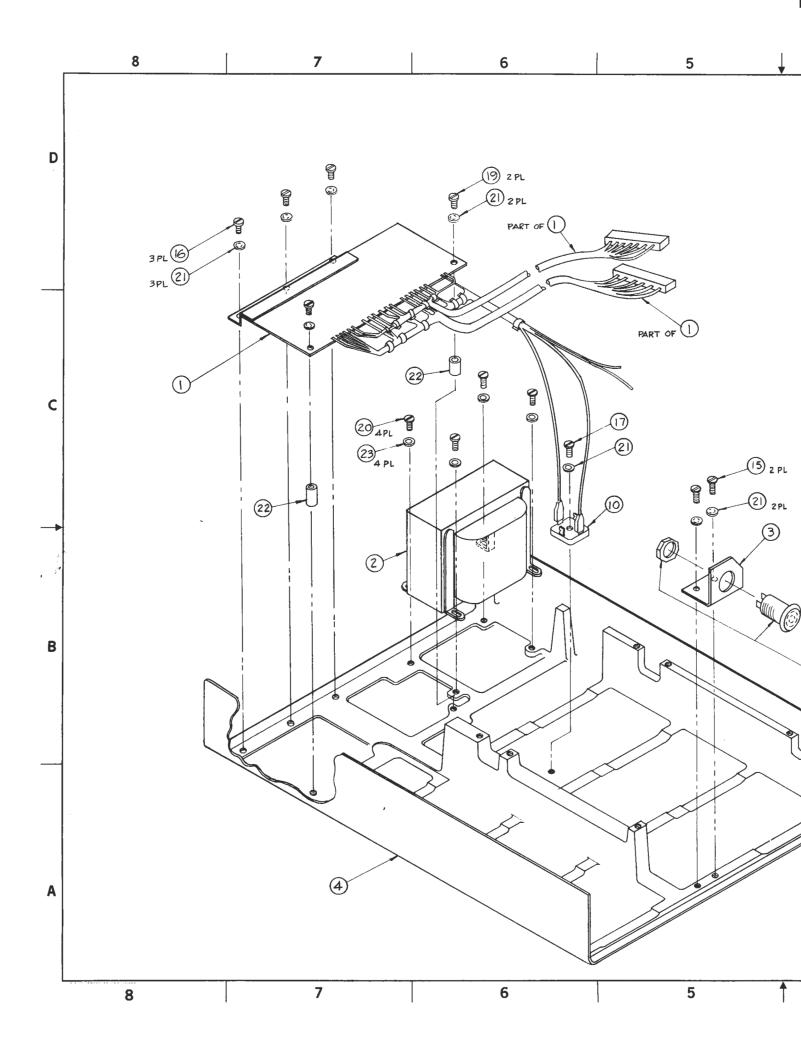

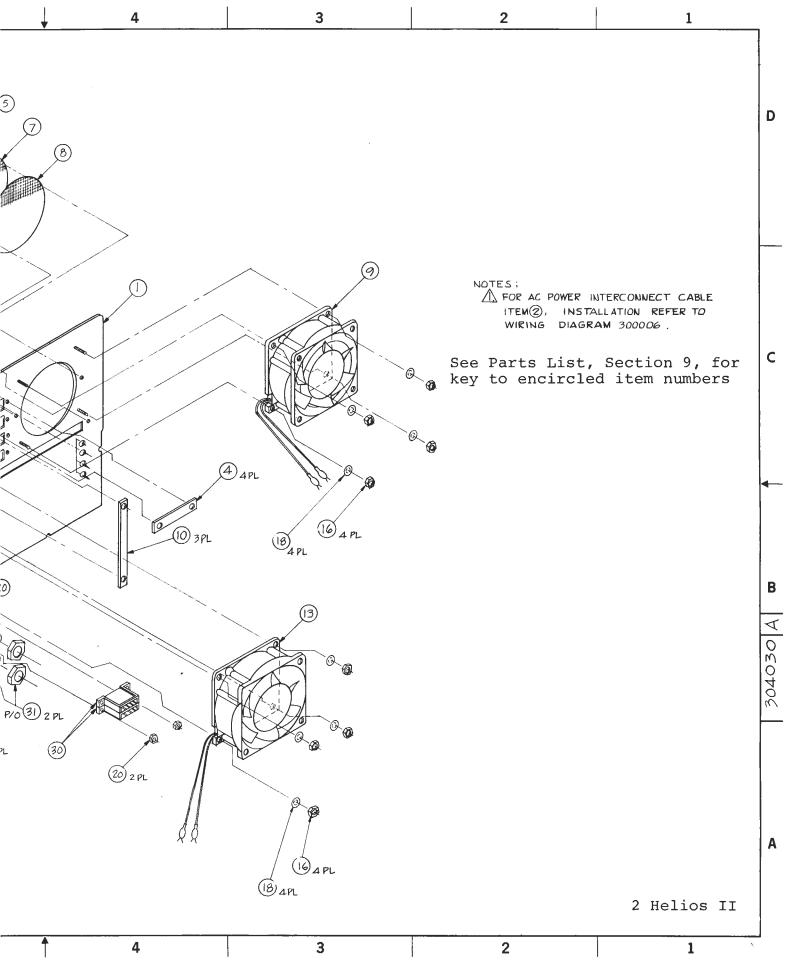

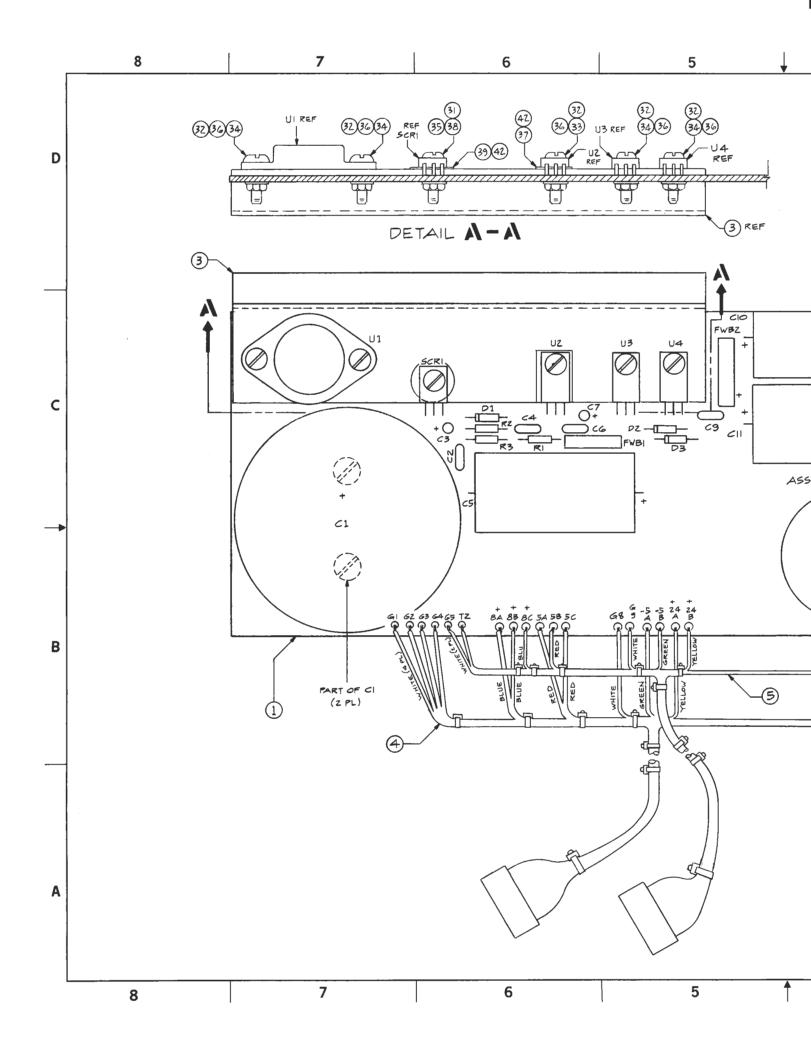

| 8-1<br>8-2<br>8-3<br>8-4<br>8-5<br>8-6<br>8-7<br>8-8<br>8-9 | System Assembly, Interconnect Diagram                                                                      | 8-1<br>8-2<br>8-3<br>8-4<br>8-5<br>8-6<br>8-7<br>8-8<br>8-9 |

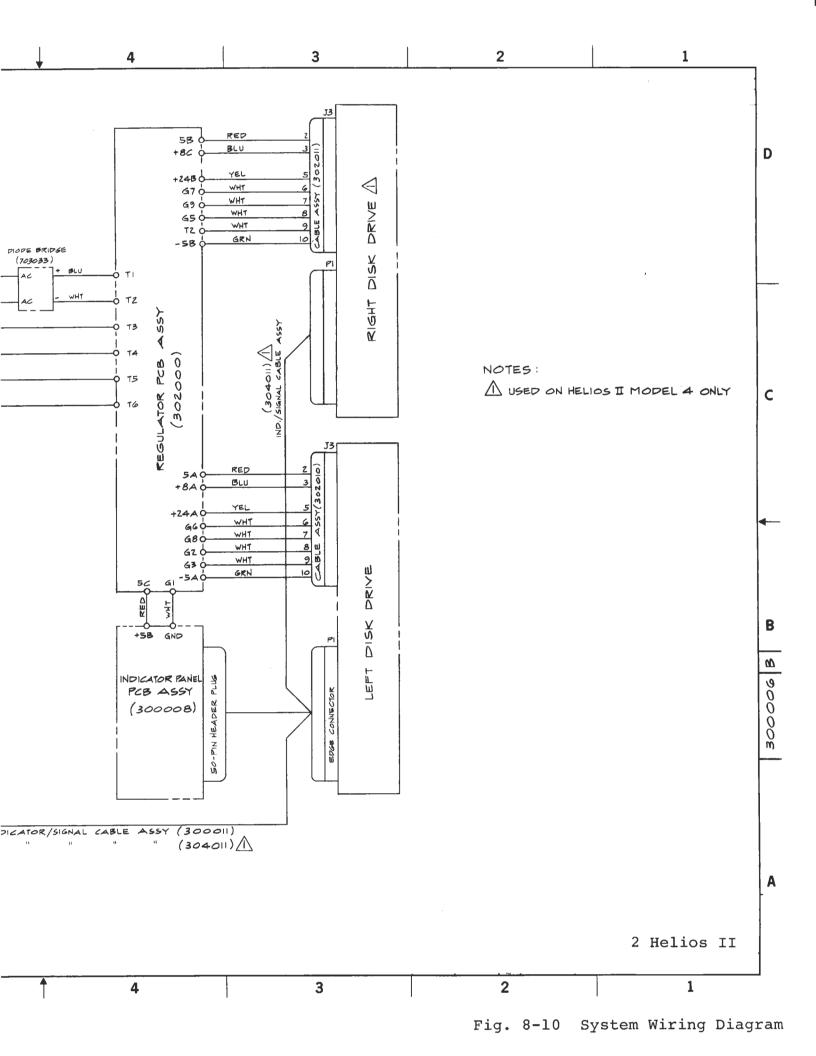

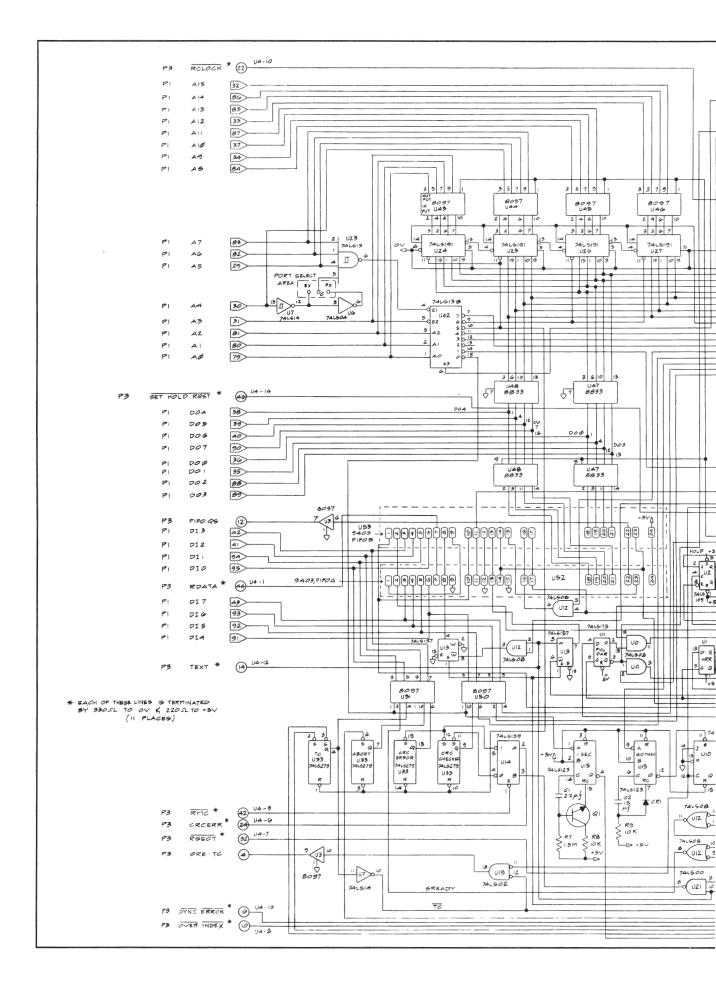

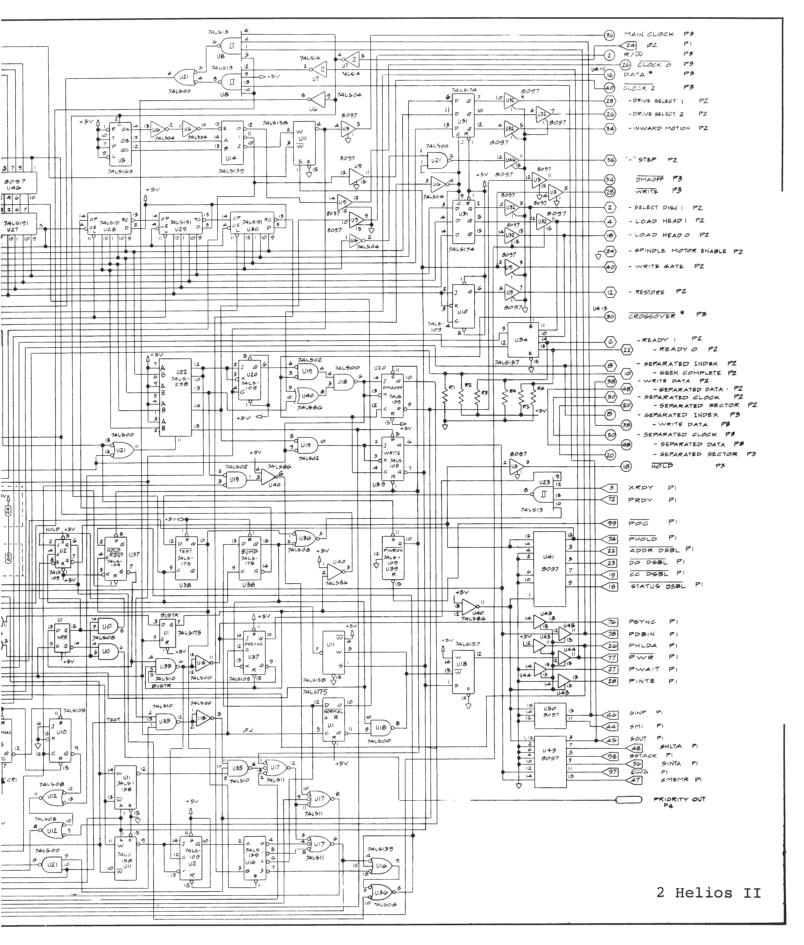

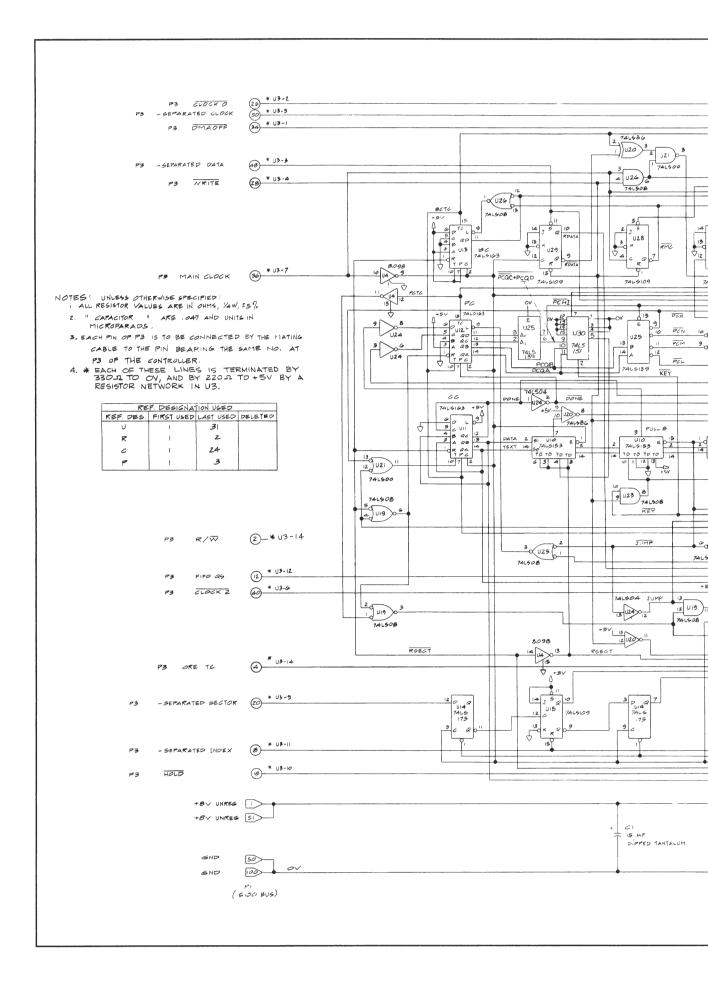

| 8-10<br>8-11<br>8-12<br>8-13<br>8-14<br>8-15                | System Wiring Diagram                                                                                      | 8-10<br>8-11<br>8-12<br>8-13<br>8-14<br>8-15                |

| 8-16<br>8-17                                                | Pin-to-Pin Signal Flow Diagram                                                                             | 8-16<br>8-17                                                |

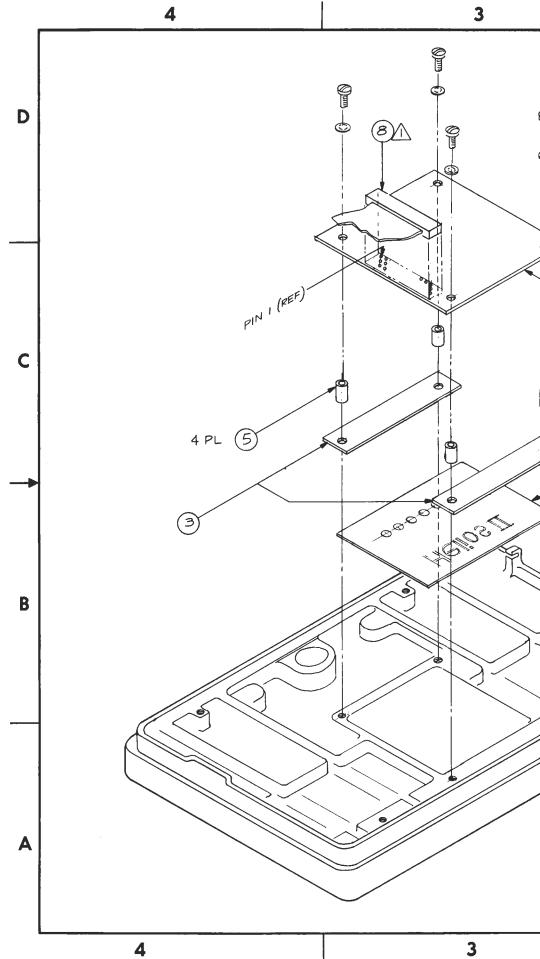

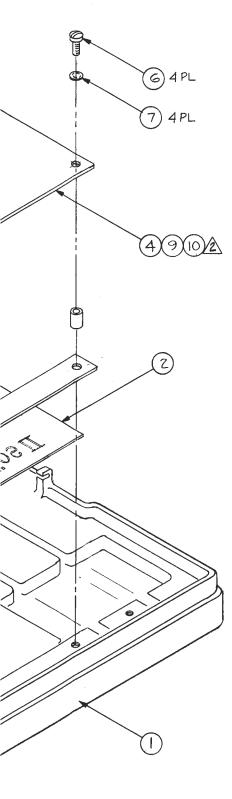

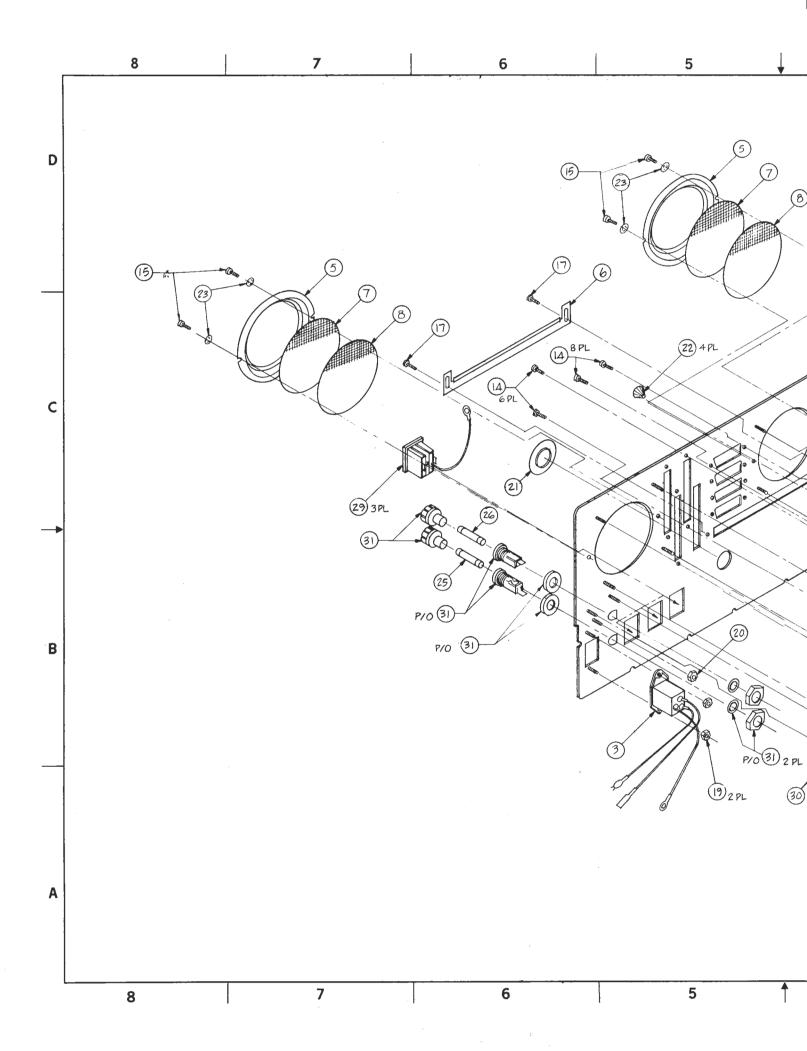

| 8-18<br>8-19<br>8-20<br>8-21<br>8-22                        | Cabinet Assembly, Model 4, Exploded Base Assembly, Model 4, Exploded                                       | 8-18<br>8-19<br>8-20<br>8-21<br>8-22                        |

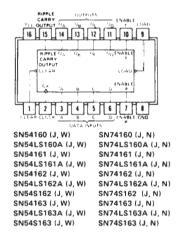

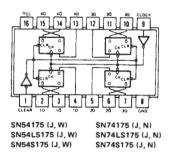

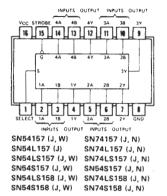

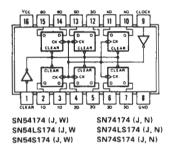

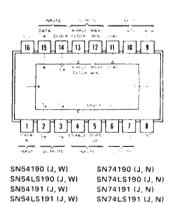

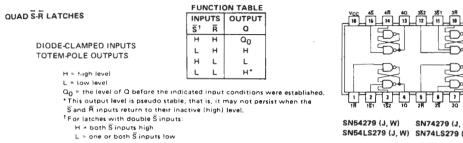

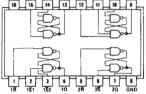

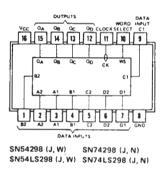

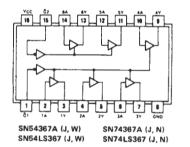

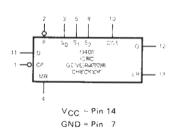

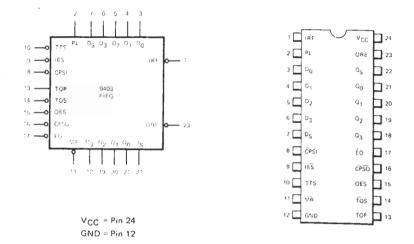

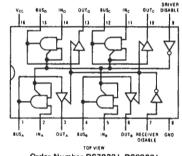

| 9-1                                                         | IC Pin Configurations                                                                                      | 9-1                                                         |

|                                                             | LIST OF TABLES                                                                                             |                                                             |

| 5-1<br>5-2                                                  | Command Port Test Pattern Bits                                                                             | PAGE<br>5-6<br>5-41                                         |

| 7-1<br>7-2<br>7-3<br>7-4<br>7-5<br>7-6<br>7-7               | Distribution of Helios II Functions                                                                        | 7 - 2<br>7 - 4<br>7 - 4<br>7 - 4<br>7 - 5<br>7 - 38         |

| 7-8                                                         | Controller and S-100 Backplane (with Descriptions).<br>Diskette Drive Power and Interface Pin Connections. | 7 - 4 2<br>7 - 6 4                                          |

| 8-1<br>8-2                                                  | Numerical Pin-to-Pin Assignments,                                                                          | Fig. 8-16                                                   |

| 8-3                                                         |                                                                                                            | Fig. 8-16<br>Fig. 8-17                                      |

|                                                             | Parts Lists                                                                                                | Sec. 9                                                      |

Helios II

ABBREVIATIONS

| <u>+</u>  | Plus or minus                          | CRC ERR | CRC Error                           |

|-----------|----------------------------------------|---------|-------------------------------------|

|           |                                        | CUTS    | Computer Users                      |

| A         | Ampere; Automatic;<br>Address          | COTS    | Tape System                         |

| AC        | Alternating current                    | CWE     | Check Write Enable                  |

| ACI       | Audio Cassette<br>Interface            |         | Signal on formatter,<br>CRC gen.    |

| ADDR DSBL | Address Disable                        | D       | Display                             |

| A/R       | As received                            | DC      | Direct Current                      |

| Assy      | Assembly                               | DI      | Data Input                          |

| Aux       | Auxiliary                              | DIO     | Diode                               |

| AWG       | American Wire Gage                     | DIP     | Dual-In-Line Package                |

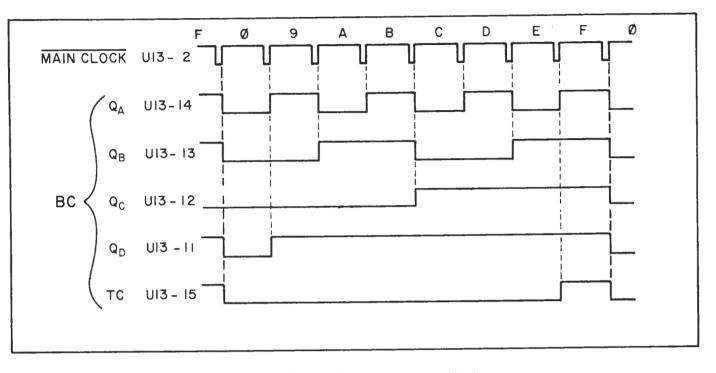

| BC        | Bit Counter                            | DMA     | Direct Memory Access                |

| BCTC      | Bit Counter transmis-<br>sion complete | DNSYNC  | Name of a FF on<br>the controller   |

| Bin       | Binary                                 | DO      | Data Output                         |

| во        | Bootload                               | DO DSBL | Data Out Disable                    |

| Br.       | Bridge                                 | DOS     | Disk Operating<br>System            |

| BTU       | British Thermal Unit                   | Drv     | Drive                               |

| BUSTR     | Bus Strobe                             | DS      | Data Serial                         |

| С         | Celsius (centigrade);<br>Capacitor     | EMI     | electromagnetic<br>interference     |

| CC        | Construction Counter                   | EO      | Enable Output                       |

| CC DSBL   | Command/Control<br>Disable             |         | (Fifo signal)                       |

| Cer       | Ceramic                                | EX-OR   | exclusive OR                        |

| CF        | Carbon film                            | F<br>   | Fahrenheit                          |

| CI        | Command Interpreter                    | Fab     | Fabrication                         |

| Cm        | Centimeter                             | FF      | Flipflop                            |

| CNTR      | Counter                                | FIFO    | First-In, First-Out<br>(LSI Buffer) |

| Comm      | Commoning                              | FIFOPL  | FIFO Parallel Load                  |

| Conn      | Connector                              | FIFO QS | Fifo Serial Output                  |

| CPSI      | Clock Pulse Serial                     | Fig     | Figure                              |

| 0101      | Input                                  | ft      | feet                                |

| CPSO      | Clock Pulse Serial<br>Output           | FW      | Flat Washer                         |

| CPU       | Central Processing<br>Unit             | g       | gravity (unit of<br>measure)        |

| CR        | Carriage Return                        | GND     | Ground                              |

| CRC       | Cyclic Redundancy                      | Hex     | hexidecimal                         |

| 2         | Check                                  | HN      | hex nut                             |

| HRR      | Hold Request<br>Resynchronized            | NPN    | Negative, Positive,<br>Negative             |

|----------|-------------------------------------------|--------|---------------------------------------------|

| Hz       | Hertz (cycle)                             | ns     | nanosecond                                  |

| IC       | Integrated Circuit                        | Ω      | ohm                                         |

| ID       | Identifier                                | OD     | outside diameter                            |

| IESA     | Input Enable<br>Serial, A                 | OESA   | Output Enable<br>Serial, A<br>(Fifo signal) |

| IESB     | INPUT Enable<br>Serial, B                 | OESB   | Output Enable<br>Serial, B                  |

| Insul.   | Insulated                                 |        | (fifo signal)                               |

| Inv      | Inverter                                  | ORE    | Output Register                             |

| I/O      | Input/Output                              |        | Empty                                       |

| IRF      | Input Register Full                       | Р      | Plug; Processor                             |

| ITLW     | Internal Tooth                            | PC     | Punctuation Counter                         |

| J        | Lock Washer<br>Jack                       | РСВ    | Printed Circuit<br>Board                    |

| JK       | Inputs to a JK                            | PCHI   | Signal on formatter                         |

|          | Flipflop                                  | PCL    | Punctuation Counter L                       |

| K<br>Kg. | kilobyte<br>kilogram                      | PCQ    | Punctuation Counter<br>Output               |

| kHz      | kilohertz                                 | PCX    | Punctuation                                 |

| LED      | Light Emitting Diode                      |        | Counter X                                   |

| LS       | Low Power Schottky                        | PDBIN  | Processor Data<br>Bus In                    |

| mA       | milliampere                               | PHLDA  | Processor Hold                              |

| μf       | microfarad                                |        | Acknowledge                                 |

| max.     | maximum                                   | PHLDAR | Delayed PHLDA                               |

| MOS      | Metal Oxide<br>Semiconductor              | PHMS   | Phillips Head<br>Machine Screw              |

| MPX      | multiplexer                               | PINTE  | Processor Interrupt                         |

| MR       | Master Reset<br>(Fifo signal)             | PL     | Enable (S-100 signal)<br>Parallel Load      |

| μs       | microsecond                               | Plex   | plexiglas                                   |

| ms       | millisecond                               | POC    | Power On Clear                              |

| MTBF     | Mean Time Between                         | PRDY   | Processor Ready                             |

|          | Failures                                  | PT     | Processor Technology                        |

| MTTR     | Mean Time To Repair                       | PTDOS  | Processor Technology                        |

| Ν        | number                                    |        | Disk Operating System                       |

| NA       | Not Applicable;<br>National Semiconductor | PWAIT  | Processor Wait<br>(S-100 signal)            |

| NET      | network                                   | PWR    | Processor Write                             |

| No.      | number                                    | Pwr    | power                                       |

|          |                                           |        |                                             |

ix

| Q      | transistor; Output of<br>a JK flipflop          | TOS          | Transfer Out Serial<br>(Fifo Signal) |          |

|--------|-------------------------------------------------|--------------|--------------------------------------|----------|

| R      | Resistor                                        | TP           | Test Point                           |          |

| RAM    | Random Access Memory                            | TR           | transfer                             |          |

| RCLOCK | Read Clock                                      | TRANS COMM   | transfer command                     |          |

| RDATA  | Read Data                                       | TTS          | Transfer to Stock,                   |          |

| Recpt. | receptacle                                      |              | FIFO signal                          |          |

| Rect.  | Rectifier                                       | U            | Integrated Circuit                   |          |

| Reg.   | regulator                                       | UFO          | Unidentified Flying<br>Object        |          |

| REV    | revision                                        | UUT          | Unit Under Test                      |          |

| RH     | Relative Humidity                               | Φ <b>2</b>   | Phase 2                              |          |

| RMC    | Read missing clock                              | . <b>.</b> . | (Signal on Controller)               |          |

| RND    | Round                                           | V            | Volt(s)                              |          |

| rpm    | revolutions per minute                          | VAC          | Volts AC                             |          |

| RSECT  | Sector Reset                                    | VCC          | +5 V<br>(Dife pin)                   |          |

| RQST   | Request                                         |              | (Fifo pin)<br>Volts DC               |          |

| R/W    | Read or Write                                   | VDC          |                                      |          |

| S      | Seek; Status                                    | VDM          | Video Display Module                 |          |

| S-100  | name of Intel standard<br>100-pin bus interface | VOM<br>XCVR  | volt/ohm meter<br>transceiver        |          |

| SREADY | Status Ready                                    | XEQ          | Execute                              |          |

| SS     | solid strand                                    | XRDY         | External Ready                       |          |

| sec.   | second                                          |              | _                                    |          |

| SHLTA  | Status Halt Acknowledge                         |              |                                      |          |

| SINP   | Status Input                                    |              |                                      |          |

| SINTA  | Status Interrupt<br>Acknowledge                 |              |                                      |          |

| Sldr   | solder                                          |              |                                      |          |

| SMl    | Status Machine Cycle l                          |              |                                      |          |

| SMEMR  | Status Memory Read<br>(S-100 signal)            |              |                                      |          |

| SOUT   | Status Output                                   |              |                                      |          |

| SWO    | Status Write Out<br>(S-100) Signal              |              |                                      |          |

| SYNC   | Synchronization                                 |              |                                      |          |

| Tant   | tantalum                                        |              |                                      |          |

| ТС     | Transmission Complete                           |              |                                      |          |

| TCSI   | Transmission Complete<br>Serial Input           |              |                                      | $\frown$ |

| TOP    | Transfer Out Parallel<br>(Fifo Signal)          |              |                                      |          |

|        |                                                 |              |                                      |          |

#### CONTENTS

# SECTION 1 INTRODUCTION

| SECTION           |                                       |            |       |      |   |   |   | PAGE |

|-------------------|---------------------------------------|------------|-------|------|---|---|---|------|

| 1.0 SCOPE OF THIS | MANUAL                                |            | • •   | • •  | • | • | • | 1-1  |

| 1.1 GENERAL DESCR | IPTION OF THE                         | Helios II  | SYSTE | м    | • |   | • | 1-1  |

| 1.2 PHYSICAL CONF | IGURATION .                           |            |       |      |   |   |   | 1-1  |

| A. Model 2 .      |                                       | • • • • •  |       | • •  |   |   |   | 1-1  |

| B. Model 4 .      | • • • •                               |            | • •   | •••  | • | • | • | 1-1  |

| 1.3 OPERATING SYS | TEM and TEST/D                        | IAGNOSTIC  | PROGR | AMS. | • | • | • | 1-2  |

| 1.4 DESCRIPTION O | F DISKETTE DRI                        | VE ASSEMBI | LY .  | • •  | • | • | • | 1-2  |

| 1.4.1 Disket      | te Access .                           |            |       |      | • |   | • | 1-2  |

| 1.4.2 Electr      | onics                                 | • • •      | • •   |      |   |   | • | 1-2  |

| 1.5 DISKETTE      | · · · · · · · · · · · · · · · · · · · |            | •     |      |   | • |   | 1-3  |

| 1.5.1 Disket      | te Interchange                        | ability .  |       | • •  |   |   | • | 1-3  |

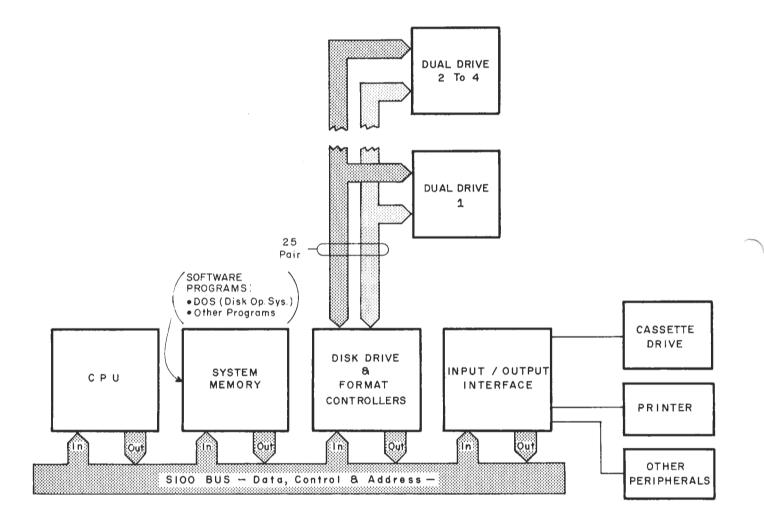

Fig. 1-1 Helios II System, Generalized Block Diagram

#### 1.0 SCOPE OF THIS MANUAL

This manual is an operating and light maintenance reference for Helios II floppy disk memory system in its various configurations. The binder containing this manual also contains the system software manual, PTDOS User's Manual.

For detailed drive assembly troubleshooting, and replacement procedures for authorized dealers, refer to <u>Helios II Service</u> <u>Manual</u>.

1.1 GENERAL DESCRIPTION OF THE Helios II SYSTEM

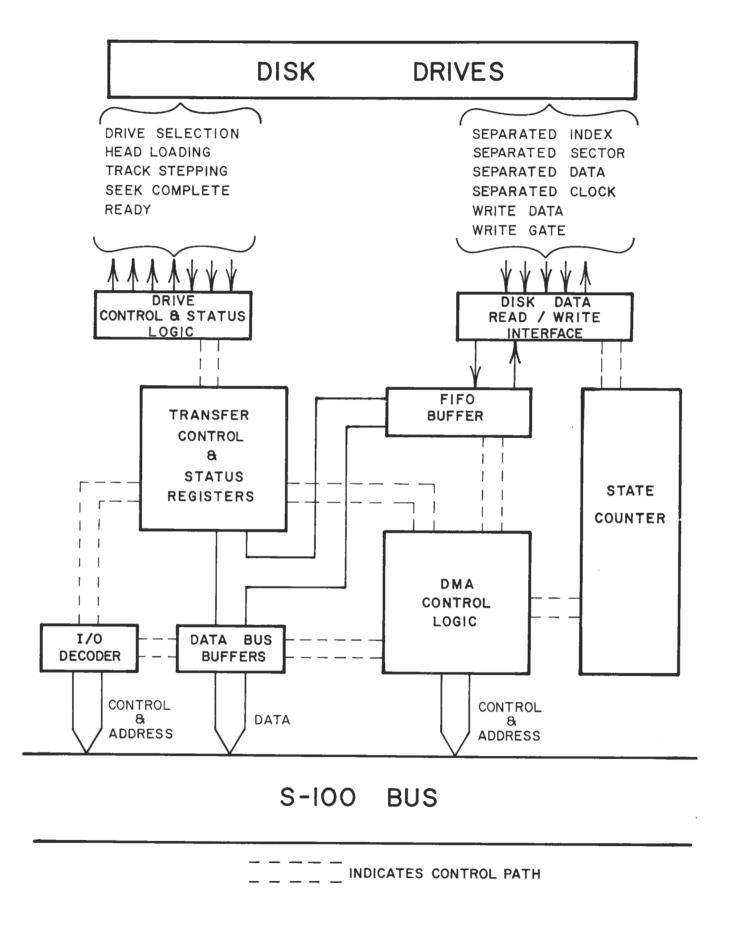

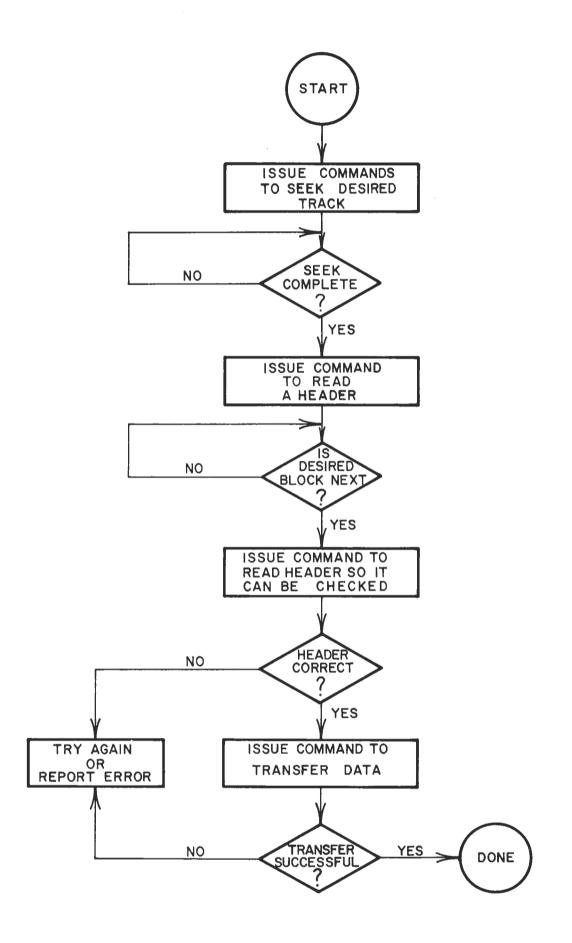

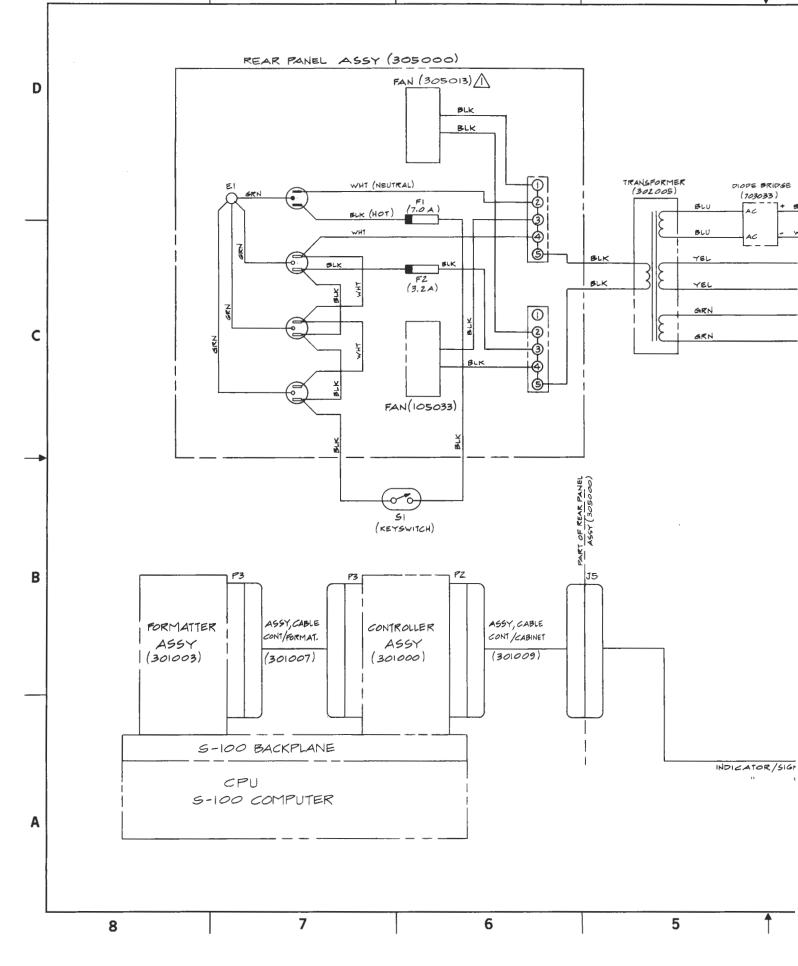

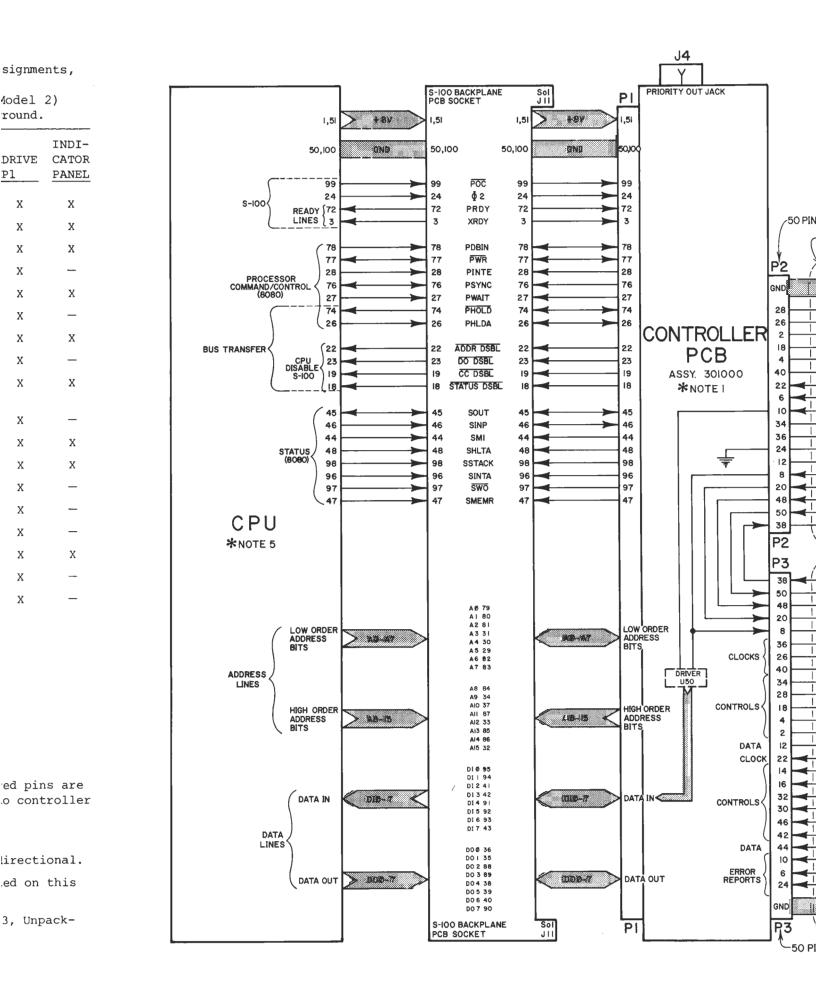

(Refer to Fig. 1-1, Helios II System, Generalized Block Diagram.)

The Helios II is a dual floppy disk drive system designed as a mass data storage for host microcomputers using the S-100 bus. The disk drive unit is a firm-sectored type, which uses an optical sector and indexing system. The diskette required is a standard 32+1 hole diskette. System storage capacity is approximately 768,768 bytes per dual drive (two diskettes). The controller in the system is capable of interfacing up to four dual drives in two cabinets. Access time is approximately 173 ms typical. DMA (Direct Memory Access) transfer rate is approximately .66 megabyte per second. A sixteen byte fifo buffers the drive and computer.

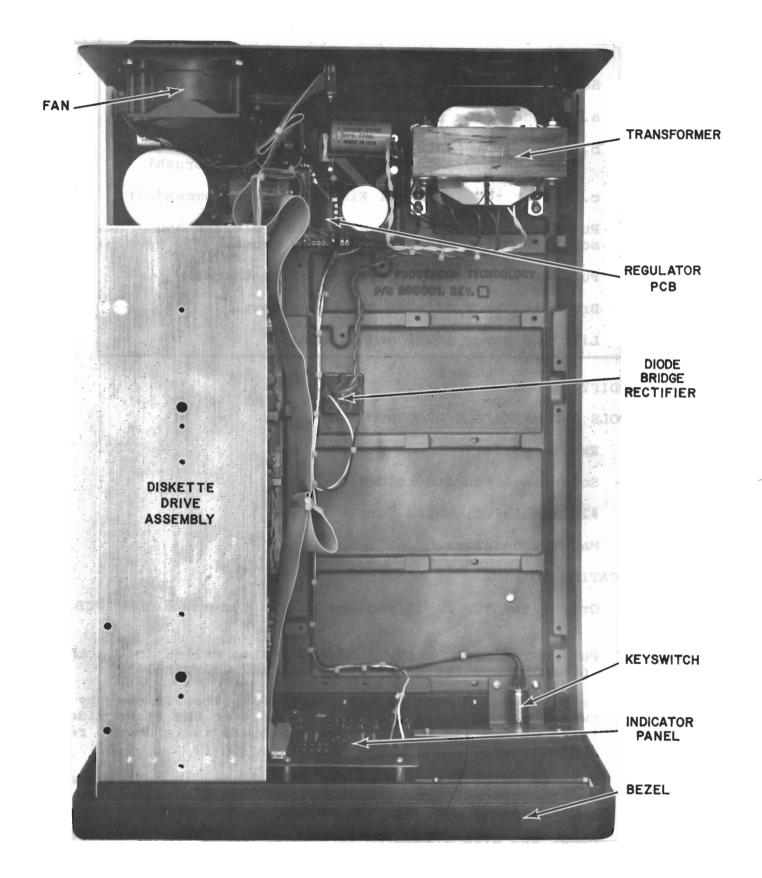

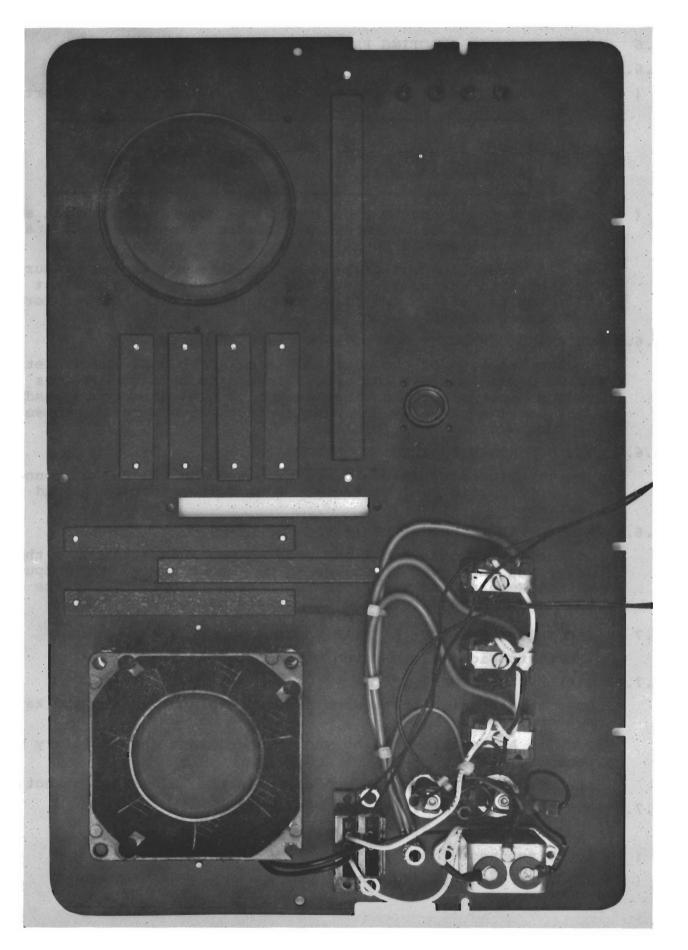

- 1.2 PHYSICAL CONFIGURATION (Refer to Fig. 3-4, Diskette Drive Cabinet, Inside View.)

- A. Model 2

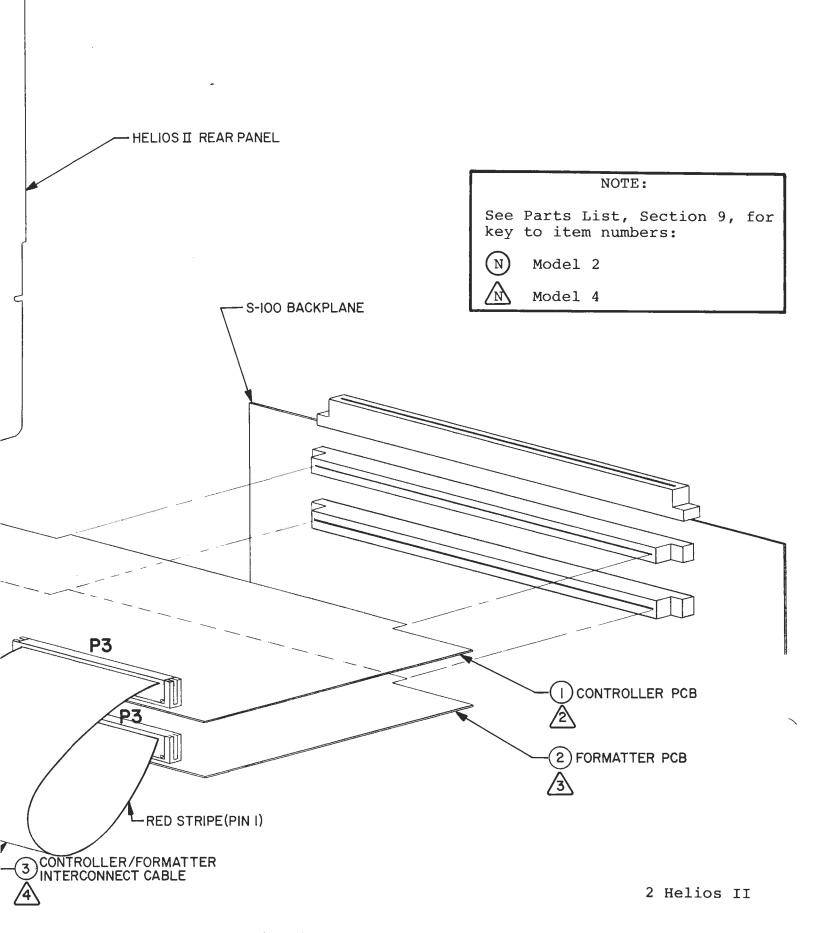

The Helios II Model 2 consists of one dual drive unit, in its own air cooled cabinet, a controller PCB and formatter PCB which plug into the backplane of the S-100 bus, a power supply and cabling. (Refer to the frontispiece "Helios II System ...") The formatter is virtually part of the controller. The formatter PCB does not have to be plugged into the backplane. A Model 2 can be upgraded to a Model 4.

B. Model 4

The Helios Model 4 consists of two dual drive units in a cabinet the same size as the Model 2. It differs from the Model 2 in that it has two fans, a higher capacity power supply, and a larger indicator display. It uses the same controller and formatter PCBs.

Two Model 4s can be daisy-chained in an 8-diskette-unit system which can be accommodated by standard controller and formatter PCBs and PTDOS software.

#### 1.3 OPERATING SYSTEM and TEST/DIAGNOSTIC PROGRAMS

A disk operating system called PTDOS (Processor Technology Disk Operating System) is provided on a diskette. A test program is also provided on cassette.

#### 1.4 DESCRIPTION OF DISKETTE DRIVE ASSEMBLY

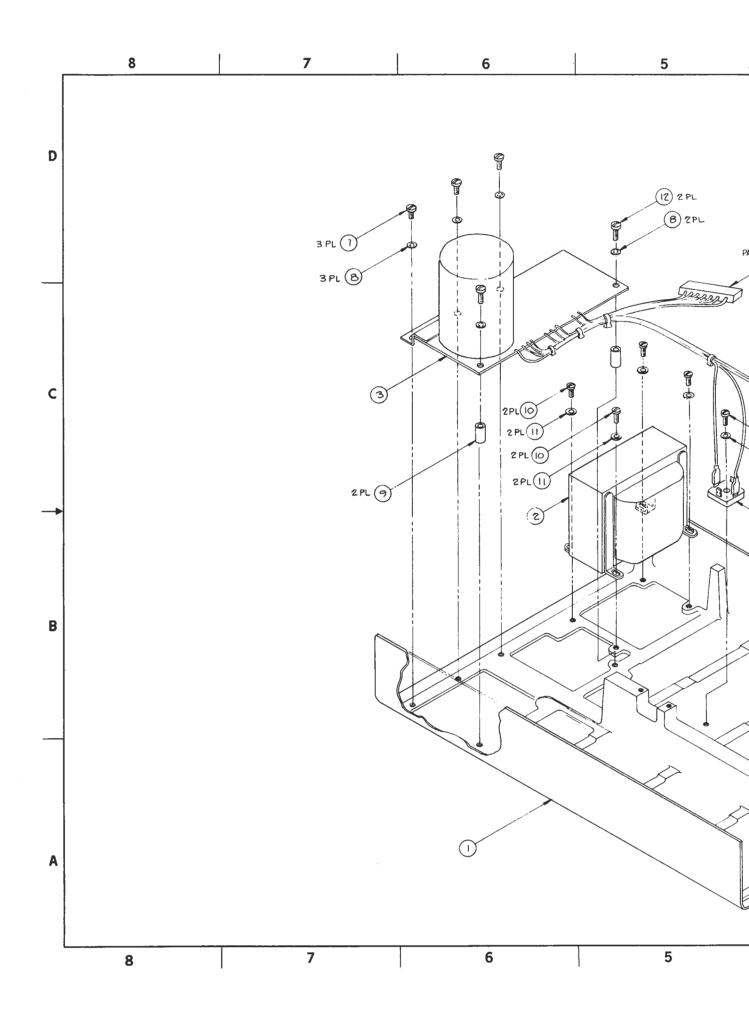

(Refer to Item 7, Fig. 8-2, Cabinet Assembly, Model 2, Exploded.)

The Helios II diskette drive assembly (commonly referred to hereafter as "drive assembly") is installed in the Helios II cabinet as a separate subassembly without DC power or cabling of its own. Signal and power are provided from interconnections from other subassemblies in the system.

The Helios II diskette drive is designed to provide a means of low-cost, random-access data storage. This is accomplished through the recording of data on, and the retrieval of data from two separate rotating magnetic surfaces, as represented by two separate diskette cartridge assemblies (commonly called diskettes).

Means for easy acceptance, rotation, and quick independent removal of each diskette is provided by spindles which are linked to and derive their rotational motion from an electrical drive motor.

The diskette drive consists of: selectable read/write/erase electronics; common positioning control electronics; a common head positioning actuator; a common Track  $\emptyset\emptyset$  sensor; a common spindle drive mechanism; two read/write/erase heads; two head loading actuators; two separate index sensors.

1.4.1 DISKETTE ACCESS

Data is transferred to or from each diskette through its separate read/write/erase head.

Each read/write/erase head is assembled on a carriage which is located on the common head positioning actuator. The read/ write/erase head is in direct contact with the diskette media surface. The head employs a single read/write gap followed by tunnel erase elements to provide erased areas between data tracks. Thus, normal track position tolerances between media and drives will not degrade the signal-to-noise ratio, and the diskette interchangeability is enhanced.

#### 1.4.2 ELECTRONICS

A. Sufficient control electronics are employed to provide minimal data access time at optimal data transfer rates within compatibility requirements.

The electronics perform the following functions:

- 1. Interpret and generate control signals.

- 2. Move the read/write/erase heads to the selected track.

- 3. Load the heads and read or write data.

- 4. Drive the spindle motor.

- B. The electronics are packaged on printed circuit boards containing the following circuits:

- 1. Head positioning actuator driver.

- 2. Head load actuator drivers.

- 3. Read/write/erase amplifier and transition detector.

- 4. Index detection.

- 5. Track position and data safety sensing.

- 6. Spindle motor driver.

#### 1.5 DISKETTE (Refer to Section 2, for specifications.)

The diskette is a cartridge that consists of a flexible magnetic disk enclosed in a plastic jacket. The disk is free to rotate within the jacket. Access and sector/index holes for the read/write/erase head and for data timing are provided. There are 32 sector holes and one index hole. Data is recorded only on one side of the diskette at the present time. The Helios II has provisions for the addition of another index photosense assembly to accommodate recording on both sides of the diskette. Reading and writing are done with the head in contact with the disk.

The diskette is provided with an envelope and container to protect the diskette when not in use. Detailed handling instructions are described in Section 4, Operating Instructions.

#### 1.5.1 DISKETTE INTERCHANGEABILITY

Each diskette drive in conjunction with the controller transfers data to and from the diskette in such fashion that diskettes are fully "write/read" interchangeable within any other Helios II diskette drive system. (See Section 4.3.3, Diskette Compatibility with Other Systems.)

# CONTENTS

# SECTION 2 SPECIFICATIONS

| SI | ECTION |         |       |         |        |       |      |     |    |   |   |   |   |   |   |   | PAGE |

|----|--------|---------|-------|---------|--------|-------|------|-----|----|---|---|---|---|---|---|---|------|

|    | 2.0    | INTROD  | UCTT  | TNC     |        |       |      |     |    |   |   |   |   |   |   |   | 2-1  |

|    |        |         |       |         | •••    | •     | •    | •   | •  | • |   | • | • | • | • | • | 2-1  |

|    | 2.1    | SYSTEM  | SPEC  | CIFICAT | IONS.  | •     | •    | •   | •  | • | • | • | • | • | • | • | 2-1  |

|    |        | 2.1.1   | Phys  | sical.  |        |       |      |     |    |   | • |   |   | • | • | • | 2-1  |

|    |        |         | Α.    | Net Sh  | ipping | y Wei | ght  |     |    |   |   |   | • |   |   |   | 2-1  |

|    |        |         | в.    | Coolin  | ıg     |       |      |     |    |   |   |   |   |   |   | • | 2-1  |

|    |        |         | с.    | Dimens  | ions.  |       |      |     |    |   |   |   | • |   |   |   | 2-1  |

|    |        | 2.1.2   | Env   | ironmen | tal .  |       |      |     |    |   |   |   |   |   |   |   | 2-1  |

|    |        |         | Α.    | Temper  | ature  | and   | Hum  | idi | ty |   |   |   |   |   |   |   | 2-1  |

|    |        |         | в.    | Ambien  | t Air  |       |      |     | •  |   |   |   | • |   |   |   | 2-1  |

|    |        |         | с.    | Other   |        |       | •    |     |    |   |   |   |   |   |   |   | 2-1  |

|    |        | 2.1.3   | Powe  | er Requ | iremer | nts   | •    | -   | •  | • |   |   |   |   |   | • | 2-1  |

|    | 2.2    | PCBs    |       |         |        |       | •    |     |    |   | • | • | • |   | • | • | 2-2  |

|    |        | A. IC   | Tech  | nnology |        |       |      |     |    |   |   |   |   |   |   |   | 2-2  |

|    |        | B. Por  | wer I | Require | ments  |       |      |     |    |   |   |   |   |   |   |   | 2-2  |

|    |        | C. Con  | nnect | tors.   |        |       |      | •   | •  | • | • | • | • | • | • |   | 2-2  |

|    | 2.3    | DRIVE A | ASSEN | IBLY .  | • •    | •     | •    | •   | •  | • |   | • | • | • | • | • | 2-2  |

|    |        | 2.3.1   | Dime  | ensions |        |       |      |     |    |   |   |   |   |   |   |   | 2-2  |

|    |        | 2.3.2   | Mult  | tiple-D | rive ( | optic | n    |     |    |   |   |   |   |   |   |   | 2-2  |

|    |        | 2.3.3   | Envi  | ironmen | tal Re | guin  | eme  | nts |    |   |   |   |   |   |   |   | 2-3  |

|    |        |         | Α.    | Temper  |        |       |      |     |    |   |   |   |   |   |   |   | 2-3  |

|    |        |         | в.    | Magnet  | ic Fie | elds  |      |     |    |   |   |   |   |   |   |   | 2-3  |

|    |        |         | с.    | Altitu  | de .   |       |      |     |    |   |   |   |   |   |   |   | 2-3  |

|    |        |         | D.    | Shock   |        |       |      |     |    |   |   |   |   |   |   |   | 2-3  |

|    |        |         | E.    | Cleanl  | iness  |       |      |     |    |   |   |   |   |   |   |   | 2-4  |

|    |        | 2.3.4   | Elec  | ctrical | Speci  | fica  | itio | ns  |    |   |   |   |   |   |   |   | 2-4  |

|    |        |         | A.    | DC Pow  |        |       |      |     |    |   |   |   |   |   |   |   | 2-4  |

|    |        |         | в.    | Logic   | Levels |       |      | -   |    |   | - |   |   |   |   |   | 2-4  |

|    |        |         |       |         |        |       |      |     |    |   |   |   |   |   |   |   |      |

# CONTENTS (Continued)

| SECTION |        |                                                              |      |     | PAGE |

|---------|--------|--------------------------------------------------------------|------|-----|------|

|         | 2.3.5  | Functional Specifications                                    |      |     | 2-4  |

|         |        | A. Diskette Loading Controls                                 |      |     | 2-4  |

|         |        | B. Diskette Rotational Speed Control                         |      |     | 2-5  |

|         |        | C. Head Loading                                              |      |     | 2-5  |

|         |        | D. Head Positioning                                          |      |     | 2-5  |

|         |        | E. Data Recording                                            |      |     | 2-6  |

|         |        | F. Data Addressing at Track Locations                        |      |     | 2-7  |

|         |        | G. MTBF, MTTR (See Section 6, Maintenance                    | è.). | • • | 2-7  |

|         | 2.3.6  | Safety Requirements                                          |      |     | 2-7  |

|         |        | A. Interlocks                                                |      |     | 2-7  |

|         |        | B. Heat Dissipation                                          |      |     | 2-7  |

|         | 2.3.7  | Interface Connectors                                         |      |     | 2-7  |

|         |        | A. Signal Interface                                          |      |     | 2-8  |

|         |        | B. Power and Interface Pin Connections .<br>(See Section 7.) |      | • • | 2-8  |

|         |        | C. DC Power to Diskette Drives                               |      |     | 2-8  |

|         | 2.3.8  | Interface Requirements                                       |      |     | 2-8  |

|         |        | A. Power-On Sequence                                         |      |     | 2-8  |

|         |        | B. Power-Off Sequence                                        |      |     | 2-8  |

|         |        | C. Data Access and Transfer                                  |      |     | 2-9  |

| 2.4     | DISKET | TE (For care and handling, see Section 4.3.                  | ).   |     | 2-10 |

|         | 2.4.1  | Physical                                                     |      |     | 2-10 |

|         |        | А. Туре                                                      |      |     | 2-10 |

|         |        | B. Wearlife                                                  |      |     | 2-10 |

|         |        | C. Dimensions                                                |      |     | 2-10 |

|         | 2.4.2  | Environmental                                                |      |     | 2-11 |

|         |        | A. Temperature and Humidity                                  |      |     | 2-11 |

|         |        | B. Ambient Air                                               |      |     | 2-11 |

|         |        |                                                              |      |     |      |

#### 2.0 INTRODUCTION

These specifications are divided into four subsections:

- System (the cabinet and the PCBs installed in the host computer and cabling).

- 2. The PCBs excluding those in the drive assembly.

- 3. The diskette drive assembly.

- 4. The diskette.

All specifications pertain to a Model 2 (one dual drive) unless noted otherwise.

- 2.1 SYSTEM SPECIFICATIONS

- 2.1.1 PHYSICAL

- A. Net Shipping Weight: 24.04 Kg. (53 lbs.)

- B. Cooling: Forced air with passive mechanical filter.

- C. Dimensions (cabinet) Height: 23.47 cm (9.24") Width: 35.59 cm (14.01") Length: 50:72 cm (19.97")

#### 2.1.2 ENVIRONMENTAL

- A. Temperature and Humidity

- 1. Operating

- a. Range: 10 to 38°C (50 to 100°F)

- b. Max. gradient: 36°C (20°F) per hour.

- c. Relative Humidity: 8 to 80%.

- d. Max. Wet Bulb Temperature: 25°C (78°F).

- 2. Storage (Non-operating)

- a. Range: -29 to +49°C (-20 to +120°F).

- b. Max. gradient: 36°C (20°F) per hour.

- c. Relative Humidity: 8 to 80%.

- d. Max. Wet Bulb Temperature: 29°C (85°F).

- B. Ambient Air: Clean, dust and particle free air, cool with 50% humidity. No corrosive gases in the air. No colloids such as tobacco smoke.

- C. Other: (See 2.3.3, Diskette Drive Assembly.)

- 2.1.3 POWER REQUIREMENTS (Cabinet with contained components, excluding PCBs in host computer.)

117 VAC, 8A Max; 5.0 nominal running

OR: 230 V, 50 Hz

Average Power Consumption: 30 watts

#### 2.2 PCBs

The following PCBs are components of the system outside of the diskette drive assembly:

- 1. Controller

- 2. Formatter

- 3. Indicator Panel

- 4. Regulator

- A. IC Technology

TTL and low power Schottky TTL.

B. Power Requirements

| PCB                                  | Voltage                                                                                                                                      | Current<br>(Typical) |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Controller<br>Formatter<br>Regulator | +8 VDC (typical) +7.25 VDC (min.)<br>+8 VDC unregulated +7.25 V (min.)<br>+8 VDC unregulated (min.); -8 V<br>60 Hz (min.); 24 V 60 Hz (min.) | 1600 mA<br>600 mA    |

| Indicator                            | +5 VDC                                                                                                                                       | 175 mA               |

C. Connectors

J2 of formatter PCB (jack which mates with P2): consists of a female shell: Molex Part No. 22-01-2015 and three pins, Molex Part No. 09-50-01114. (P2 is not supplied; see Section 3.5, Optional DC Power for Formatter PCB.)

2.3 DRIVE ASSEMBLY (Removed from cabinet and system)

#### 2.3.1 DIMENSIONS

Height: 21.84 cm (8.6")

Width: 11.18 cm (4.4")

Depth: 38.1 cm (15.0") overall from mounting surface

Weight (shipping): 11.34 Kg. (25 lbs. max.)

Weight (installed): 9.07 Kg. (20 lbs. max.)

#### 2.3.2 MULTIPLE-DRIVE OPTION

The multiple-drive option provides for the operation from one controller and two power supplies of up to four dual diskette drives (8 drive units) in close physical proximity to each other. All diskette drives in this system configuration use the same printed circuit boards. However, the line-terminating resistors on the diskette drive electronics printed circuit board (Data and Interface PCB) and indicator panel PCBs and are removed from all but the drive farthest from the controller, and the proper drive selector module is inserted in each drive. (Refer to Section 4.2.2, Drive Configuration.)

#### 2.3.3 ENVIRONMENTAL REQUIREMENTS:

The diskette drive and diskette should be in the same environment and subject to the same environmental conditions (especially temperature and humidity) for at least one hour prior to operation, as normal recommended operating procedure.

A. <u>Temperature</u>, <u>Relative Humidity</u>, <u>Maximum Wet Bulb</u> (See Section 2.1.2, System Environmental.)

#### B. Magnetic Fields

1. Operating

The ambient stray magnetic field in the region of the head should not exceed 15 Gauss.

2. Storage

The ambient stray magnetic field in the region of the diskette should not exceed 50 oerstads.

- C. Altitude

- 1. Equipment Operational

Sea level to 10,000 feet.

2. Equipment Non-operational

Sea level to 35,000 feet.

#### D. Shock and Vibration

The equipment should not suffer damage nor fail to perform as specified after having been subjected to the following shock and vibration under non-operational conditions:

1. Shock

Internal bracing is allowed if needed to meet this requirement. Eighteen (18) impact shocks of 5 g's  $(\pm 10\%)$ consisting of three shocks in opposite directions along each of three mutually perpendicular axes. Each shock impulse shall be a half sine wave with a time duration of 11  $(\pm 1)$  ms.

2. Vibration

Internal bracing is allowed, if needed, to meet this requirement. 1.5 g's  $(\pm 10\%)$  for the 5 to 55 (Hz) range for four hours on each axis with a 20-minute frequency scan.

#### E. Cleanliness

The Helios II diskette drive assembly is designed for use in commercial and industrial environments. However, no air filters or forced-air systems are provided within the diskette drive itself. Therefore, it should be kept in the Helios cabinet. If it must be removed from the cabinet for maintenance, and operated, optimum performance can be expected when used in a computer room environment with the resultant air cleanliness found in such a location. Dust and other airborne contaminants are a major threat to the operating life of the media and drive recording and positioning systems. (Refer to Section 6, Maintenance.)

#### 2.3.4 ELECTRICAL SPECIFICATIONS

A. DC Power

The following DC power is required per dual diskette drive:

| +5V DC = 5%                                  | 1.7 A nominal running.<br>2.2 A maximum running.                                                                                                                               |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| +8V DC Unregulated<br>(Limits: 7.0 to 10.0V) | <pre>1.2 A nominal running. 2.0 A maximum running.</pre>                                                                                                                       |

| -5V DC = 10%                                 | 0.15 A nominal.<br>0.20 A maximum.                                                                                                                                             |

| +24V DC + 10%                                | <pre>1.0 A nominal when seeking.<br/>0.2 A nominal when not seeking.<br/>1.2 A maximum seeking with 3.0 A.<br/>maximum peak surges for up to<br/>10 ms at start of seek.</pre> |

#### B. Logic Levels

Interface line logic levels are as follows:

Negative level = 0.0V to  $\pm 0.5V$ . Positive level =  $\pm 2.5V$  to  $\pm 5.5V$  or open circuit. I/O signals are negative when selected (True).

#### 2.3.5 FUNCTIONAL SPECIFICATIONS

#### A. Diskette Loading Controls

Diskette loading and unloading is under manual operator control. Loading and unloading mechanisms within the drive provide the following features:

- 1. Positive diskette registration when loaded.

- Visible, partial ejection of the diskette when unloading.

- Minimum possibility of diskette damage due to loading/ unloading.

- 4. Easy diskette loading and unloading.

- 5. Unloading initiated manually or by remote control line (remote on designated options only).

- B. Diskette Rotational Speed Control

- 1. Spindle Drive System

A direct-coupled DC spindle motor servoed to follow a reference frequency comprises the diskette spindle drive system. Spindle power is applied by inserting one or both diskettes into the diskette drive.

- 2. Motor Speed Regulation

- a. Average Diskette Rotational Speed: 360 ±7 rpm

- b. Instantaneous Speed Variation: ±5 rpm

- 3. Motor Start Time

The diskette drive comes up to speed and attains operational status with 1 second after the application of drive DC or diskette insertion.

- C. Head Loading

- 1. Head Engage Time

The head engage time is less than 40 ms.

2. Head Contact Force

The head-to-disk contact force is 13 grams nominal, as established by testing and vendor recommendations.

- D. Head Positioning

- 1. Head Positioning Times

Track-to-track, including settling time: 10 ms max. Inside-to-outside track, including settling: 100 ms max.

2. Rotational Latency

Average rotational latency: 83.3 ms.

3. Head Positioning Error Rate

The head positioning error rate is less than one positioning error per  $10^6$  seek executions.

#### E. Data Recording

#### 1. Recording Mode

Data is represented on the diskette by 8-bit bytes.

#### 2. Recording Format

Firm-sectored type, formatted by PTDOS (Refer to Section 7, Theory of Operation.)

#### 3. Recording Density

Data is recorded at a nominal density of 6536  $(\pm 4\%)$  flux changes per inch for an all 1's pattern on the innermost track, and 3672  $(\pm 4\%)$  flux changes per inch for an all 1's pattern on the outermost track.

#### 4. Recording Capacity

Unformatted data capacity is 3.1 megabits per diskette and 41 kilobits per track, single-side recording. Seventy-seven (77) tracks are available.

5. Write Data Transfer Rate

The write data bit rate is determined by the controller. The nominal bit rate is 250 kilobits per second. To insure that the recording density and read data bit rate are held within the specified limits, the write data bit rate shall not vary more than  $\pm 0.3\%$  from nominal.

#### 6. Read Data Transfer Rate

The read data bit rate is determined by the recording density and the rotational speed of the diskette being read. The nominal bit rate is 250 kilobits per second. Due to variations between diskette drives and controllers, this bit rate may vary as much as ±17% on an instantaneous basis (including pulse crowding effects).

#### 7. Recoverable Read Error Rate

A recoverable read error is defined to be a read error corrected by no more than three attempts to read the record in error. The recoverable read error rate is less than one error per  $10^9$  bits read. All error rates are quoted for reading and writing on the same machine without removal and re-insertion of the diskette. All error rate tests are to be performed with a new (unused) diskette.

#### 8. Non-recoverable Read Error Rate

A non-recoverable read error is defined to be a read error which cannot be corrected after three attempts to read the record in error. The non-recoverable read error rate is less than one error per 10<sup>12</sup> bits read. Errors caused by the diskette (i.e., due to surface flaws, etc.) shall not be included in the computation of the non-recoverable read error rate.

#### F. Data Addressing at Track Locations

The diskette drive is designed to locate data at the 77 defined tracks on the initialized surface of a diskette. Recorded tracks after tunnel erasure are 0.012" on 0.021" centers. The 77 tracks are numbered from  $\emptyset\emptyset$  for the outermost track to 76 for the innermost track. Track centerline is defined by the formula:

centerline radius = 2.029" + (76-N)/48"

±(tolerance)"

where N is the physical track number.

G. MTBF, MTTR: (See Section 6, Maintenance.)

#### 2.3.6 SAFETY REQUIREMENTS

#### A. Interlocks

An interlock indicating that a diskette has been properly mounted in the diskette drive is provided for each individual unit within the dual drive. This interlock inhibits operation of the spindle motor and generation of the Ready interface signal when diskettes are not properly mounted in the diskette drive.

B. Heat Dissipation

Nominal heat dissipation for the all-DC-power diskette drive is 109 BTU per hour. Average operating power is 28 watts.

#### 2.3.7 INTERFACE CONNECTORS

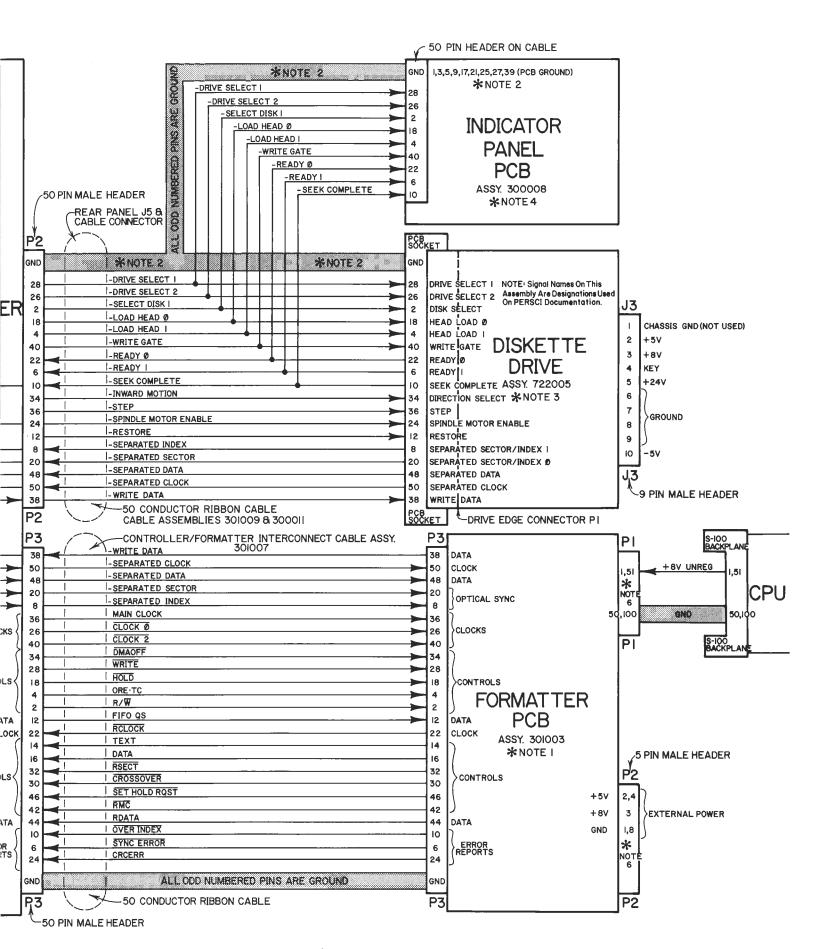

Within the configuration of a diskette system, all diskette drives are connected to the controller through a signal connector, either directly or by cabling routed in parallel to other diskette drives. Power is supplied to each diskette drive through a separate power connector.

#### A. Signal Interface

(For names and descriptions of signals, see Section 7, Theory of Operation.)

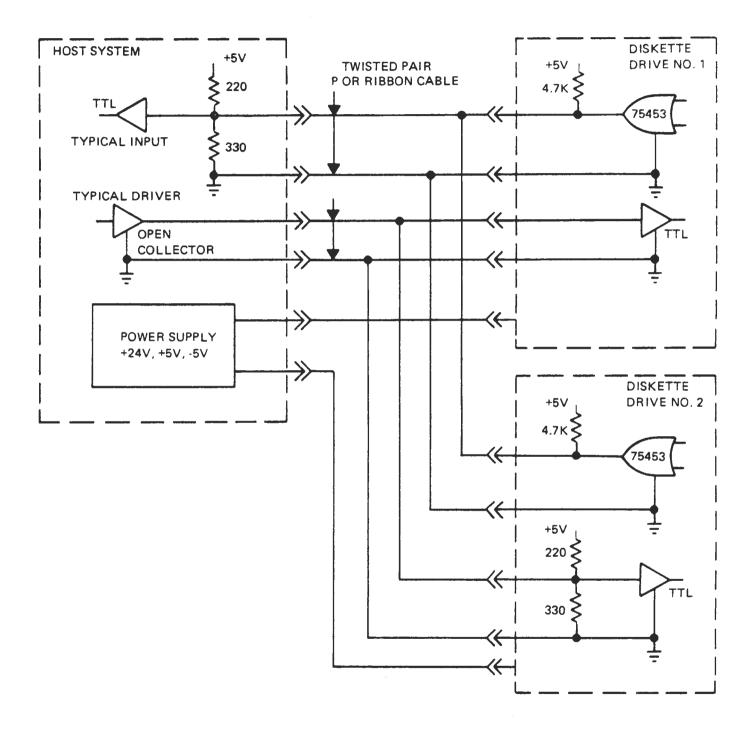

The signal connector of the first diskette drive in a diskette system is connected directly to the controller through a 50-conductor flat cable, or through a cable consisting of twenty-five twisted wire pairs. The signal connectors of subsequent diskette drives are connected in parallel with the signal connector of the first diskette drive through similar cables.

All signal lines should have a maximum length of 20 feet, and shall use a wire diameter equivalent to AWG #30 or larger.

B. Power and Interface Pin Connections

(See Section 7, Theory of Operation.)

C. DC Power to Diskette Drives

All DC power lines shall have lengths and wire diameters consistent with meeting the power regulation requirements of the diskette drive, as specified in Paragraph 2.3.4.

Eight lines are used to transmit DC power from the power supply through a separate power connector for each drive. One line pair (high and ground) is used for +5 VDC, one for +5 VDC unregulated, one for +24 VDC, and one for -5 VDC. In addition, a separate single line is available to connect drive and power supply chassis grounds.

Five-foot lengths of #18 AWG wire are normally acceptable for use as DC power lines between the drive and typical power sources.

#### 2.3.8 INTERFACE REQUIREMENTS

#### A. Power-on Sequence

DC power levels may be applied in any sequence to the diskette drive without causing damage to the drive unit.

#### B. Power-off Sequence

Power levels may be removed in any sequence from the diskette drive without causing damage to the drive.

#### C. Data Access and Transfer

The timing inter-relationship during head positioning, head selection, and data transfer satisfies the following criteria and remains within the tolerances specified below:

- 1. Diskette spindle speed: 360 ±12 rpm.

- Maximum head positioning time for an adjacent rack seek: 10 ms.

- Maximum head positioning time for a 76-track seek: 100 ms.

- 4. Average rotational latency: 83.3 ms.

- 5. Maximum motor start time: 1 sec.

- Radial dimensions of recording tracks: 3.612" for track ØØ, 2.029" for track 76.

- 7. Separation between the read/write gap and the trailing erase gap: 0.035  $\pm$  0.002".

- 8. Index pulse interval time: 166.7 ± 3.3 ms.

- 9. Read data cell time: 4.0  $\mu$ s ± 4%.

- 10. Write clock pulse to write data pulse: 2.0  $\mu$ s ± 0.3%.

- 11. Width of Read, Separated Data, and Separated Clock

pulses: 200 ns ± 20%.

- 12. Write data frequency: 249.7 kHz ± 0.3%.

- 13. Head load time: 40 ms maximum.

- 14. Erase gate turn-on: 210 ± 8 µs after leading edge of Write Gate (internal drive timing).

- 15. Erase gate turn-off: 518  $\pm$  10  $\mu$ s after trailing edge of Write Gate (internal drive timing).

- 16. Maximum rise and fall time of interface pulses: 25 ns.

- 17. Phase-locked oscillator acquisition (lock-up) requirement is 4 bytes of all zeroes data.

- 18. Separated clock contains only those clocks that were written on the diskette.

- 19. Write current amplitude automatically switched by internal drive logic between Tracks 43 and 44.

- 20. Restore is a low-speed head positioning operation to Track  $\emptyset \emptyset$ . Completion of the Restore command is indicated by a negative level on the Seek Complete interface line.

- 21. Track position incrementing of the Track Difference Buffer Register in the drive is initiated by the positive-going (trailing) edge of the internal track detent pulse.

- 22. The Direction Select line shall be stable for a minimum of 100 ns prior to the leading edge of the Step pulse(s).

- 23. The entire pulse train on the Step line representative of a multi-track address change (one pulse per track) must be transmitted in less than 2.0 ms, at pulse recurrent frequencies of up to 500 kHz.

- 2.4 DISKETTE (For care and handling of diskettes, see Section 4.3.)

- 2.4.1 PHYSICAL

- A. Type

Compatible to Dysan Part No. 101, having 32 sector holes and one index hole. Compatible diskettes are manufactured by Maxell.

B. Wearlife

200 hours of use on one track.

| с. | Dimensions | Inner Disk:        | 19.8 cm diameter (7.8") |

|----|------------|--------------------|-------------------------|

|    |            | Protective Jacket: | 20.32 cm square (8")    |

|    |            | Index Holes:       | .025 cm (.01")          |

#### 2.4.2 ENVIRONMENTAL

- A. Temperature and Humidity

- 1. Operating

(See System Environmental, 2.1.2.)

- 2. Storage (Non-operating)

- a. Range: 4°C to 53°C (40°F to 127°F).

- b. Relative Humidity: 8% to 80%.

- c. Max. Wet Bulb Temperature: 29°C (85°F).

- 3. Transportation

(Diskette in its envelope and in a protective box)

Range: -40°C to 53°C (-40 to 127°F).

Relative Humidity: 8 to 80%.

B. Ambient Air

Clean, dust and particle free air, cool with 50% humidity. No corrosive gases in the air. No colloids such as tobacco smoke.

## CONTENTS

# SECTION 3 UNPACKING AND ASSEMBLY TIPS

| SECTION | I                                   | PAGE |

|---------|-------------------------------------|------|

| 3.0     | INTRODUCTION                        | 3-1  |

| 3.1     | UNPACKING                           | 3-1  |

| 3.2     | ASSEMBLY TIPS                       | 3-2  |

|         | 3.2.1 Printed Circuit Boards        | 3-2  |

|         | A. Orientation of PCBs              | 3-2  |

|         | B. Identifying Revision Levels      |      |

|         |                                     | 3-2  |

|         |                                     | 3-3  |

|         |                                     | 3-3  |

|         |                                     | 3-3  |

|         |                                     | 3-3  |

|         |                                     | 3-4  |

|         | B. Loading ICs                      | 3-4  |

|         | 3.2.4 Soldering                     | 3-5  |

| 3.3     | MODIFYING PCBs                      | 3-7  |

|         | 3.3.1 Tools And Materials Required  | 3-7  |

|         | 3.3.2 Locating IC Pins              | 3-7  |

|         | 3.3.3 To Cut A Trace                | 3-9  |

|         | 3.3.4 To Install A Solder Bridge    | 3-9  |

|         | 3.3.5 Check after Mods              | 3-9  |

| 3.4     | RE-INSTALLING THE DISKETTE ASSEMBLY | 3-9  |

| 3.5     | OPTIONAL DC POWER FORMATTER PCB     | 3-12 |

#### 3.0 INTRODUCTION

This section contains information you may need from time to time for making hardware modifications and updates to your Helios. It includes PCB and IC handling, soldered and PCB modifying tips.

Instructions for hardware changes are in the form of Change Notices which are contained in Section 10, Updates. From time to time additional Change Notices may be sent to you.

Also, in this section are instructions for re-assembling the Helios II after special cleaning procedures in Section 6, Maintenance.

#### 3.1 UNPACKING

- 1. Choose a clear, clean, flat area to unpack.

- 2. Inspect for shipping damage. If damage is detected, contact the carrier and Processor Technology immediately.

- Do not pull the cardboard dummy diskettes out of the diskette slots. Wait until you have read Section 4, Operating Instructions. The cardboard must be ejected by the drive when AC power is applied.

- Check the contents of the shipment against the following list and the packing list. If an item is missing, notify Processor Technology.

- a. Helios II cabinet(s) with 2 keys.

- b. Controller PCB.

- c. Formatter PCB.

- d. Cable Assembly, Controller/Formatter.

- e. Cable Assembly, Controller/Cabinet(s).

- f. Helios II Disk Memory System Manual (this Manual).

- g. PTDOS User's Guide software manual

(in this binder, behind the white cardboard divider).

- h. Diskette, containing PTDOS.

- i. Diskette, blank.

- j. Cassette, Disk System Test.

NOTE: If you have purchased a computer system containing one or more Helios II cabinets, compare the contents of the shipment package(s) against the packing list instead of the above list.

There should also be an accessories price list and a warranty card in the binder of the manual.

- 5. Fill out the warranty card and mail it to Processor Technology.

- 6. When you are unpacked, go to Section 4, Operating Instructions.

#### 3.2 ASSEMBLY TIPS

- 3.2.1 PRINTED CIRCUIT BOARDS

- A. ORIENTATION OF PCBs (Refer to the PCB Assembly drawings in Section 8, Drawings.)

Orient the PCB with the component side up, lying flat on the work bench, so that the printed matter on the component side is in normal reading position. The printed matter is called the legend. The legend contains the silkscreened component layout lines and the component identification words and numbers. The components are soldered in place over their respective outlines. There may or may not be traces on the component side in addition to the components. This side of the PCB is referred to as the "component side" or the "legend side."

The opposite surface of a PCB has trace circuits etched on it and is called the "trace side," or "circuit side," or "solder side." It is characterized by a lack of components and by the points of the component lead wires protruding above its surface (when assembled).

- B. IDENTIFYING REVISION LEVELS OF ASSEMBLIES

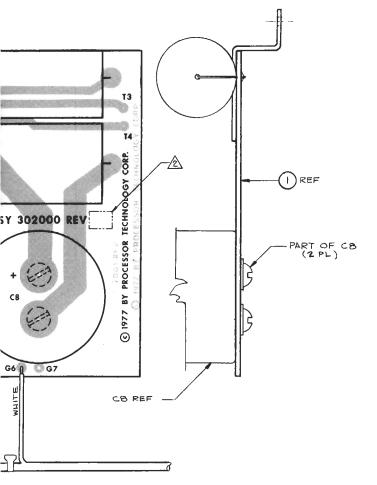

- 1. Assembly Number

This number is marked on the component side of the PCB, either silkscreened as part of the legend or etched as part of the conductor pattern if a legend is not used. Example: "ASSY 123456 REV..." The revision level is marked separately and is not part of the silkscreen or etching. "Assembly" means the board is assembled with components to a certain configuration. The same schematic may be used for different assemblies or revision levels.

2. PC Number

This number (with Rev. letter) is etched on the solder side (trace side) of the PCB. Example: "PC 123456 REV X." This PC number gives the part number and revision level of the bare board.

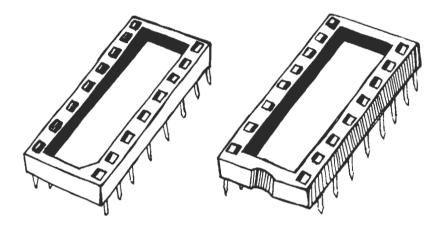

# 3.2.2 DIP SOCKETS

There are two sizes: 14 and 16-pin. The correct size is indicated by the size of the legend on the component side of the PCB.

A. Orientation of DIP Sockets

Orient each socket with its end notch or #1 end matching the colored dot on the legend. The pin #1 end is indicated by the lower right-hand corner being filled in on an angle. Occasionally, the #1 pin end of a socket is indicated instead by a notch in the side of the socket. (See Figure 3-1, DIP Sockets.)

Figure 3-1, DIP Sockets

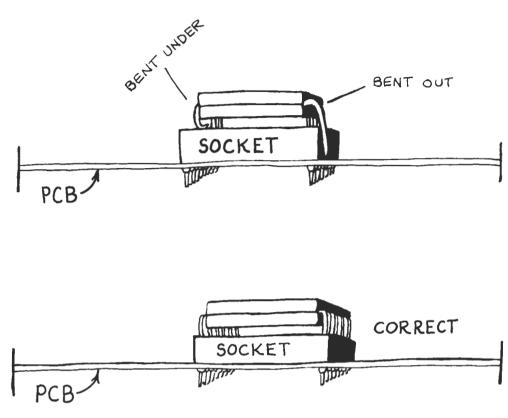

- B. DIP Socket Installation Tip

- Insert socket pins into the mounting pads at the appropriate location.

- 2. While pressing the socket in place to ensure that is is fully seated, on back (solder) side of board, bend pins at opposite corners of socket (e.g., pins 1 and 9 on a 16-pin socket) outward until they are at a 45° angle to the board surface. This secures the socket until it is soldered.

- 3. Repeat this procedure with each socket until all are secured to the board.

- 4. Solder the unbent pins on the trace side.

3-3

5. Straighten the bent pins and solder. Do not solder bent pins since that may cause solder bridges.

# 3.2.3 INTEGRATED CIRCUITS

#### CAUTION

Installing and Removing Integrated Circuits\* NEVER install or remove integrated circuits when power is applied to the Helios II. To do so can damage the ICs.

\*There are no MOS ICs on Helios PCBs.

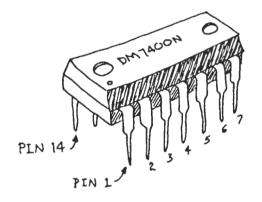

# A. ORIENTATION OF ICS AND SOCKETS

Orient the IC so that the number one pin is in the lower right hand corner. The pin number one position is indicated by a dot or small hole embossed into the lower right hand corner or by a notch molded into the IC on the lower edge when the IC is properly oriented. The assembly drawing and the legend both show the notch in the lower edge of the IC and a dot on the PCB in front of the outline of the IC socket. (See Figure 3-2, "Integrated Circuits.")

Figure 3-2, Integrated Circuits

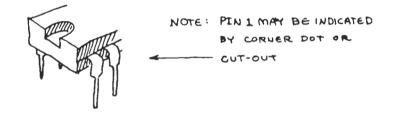

# B. LOADING ICs

Many DIP devices have their leads spread so that they may not be inserted directly into their sockets. They must be "walked in" using the following procedure.

Insert the pins from one row only into the socket until they barely engage. Push the device using both hands with even pressure to bend this first row of pins until the second row of pins lines up with the holes in the socket, then push the second row of pins into the socket. After all ICs are inserted, examine each to make sure that no pins are bent out or under. Careful examination might prevent hours of unnecessary troubleshooting later.

Figure 3-3, Checking IC Pins

# 3.2.4 SOLDERING

Use a low-wattage iron with a small screwdriver pointed tip, 25 watts maximum on the formatter, controller, and indicator panel PCBs. A higher wattage may be used on the regulator board.

Larger irons run the risk of burning the printed-circuit board. Don't try to use a soldering gun, they are too hot.

- To make a good solder joint the iron must be clean. Keep a damp piece of sponge by the iron and wipe the tip on it before using it and after each use.

- Use only 60-40 rosin-core solder. NEVER use acid-core solder or externally applied fluxes. Use the smallest diameter solder you can get.

- 4. To solder, wipe the tip, apply a light coating of new solder to it, and apply the tip to both parts of the joint, that is, both the component lead and the printed-circuit pad. Apply the solder against the lead and pad being heated, but not directly to the tip of the iron. Thus, when the solder melts the rest of the joint will be hot enough for the solder to "take," (i.e., form a capillary film).

- 5. Always heat both parts that are to be soldered, preferably at their junction. Use a very light touch. Pressing the

tip of the iron too hard on pad or trace can cause the pad or trace to lift off the board and permanently damage the board.

- Apply solder for a second or two, then remove the solder and keep the iron tip on the joint. The rosin will bubble out. Allow about three or four bubbles, but don't keep the tip applied for more than ten seconds.

- 7. Solder neatly and as quickly as possible. Wipe residual flux off the soldering iron with a damp sponge.

- 8. Solder Bridges

Solder should follow the contours of the original joint. A blob or lump may well be a solder bridge, where enough solder has been built upon one conductor to overflow and "take" on the adjacent conductor. This causes a short circuit. Due to capillary action, these solder bridges look very neat, but they are a constant source of trouble when boards of a high trace density are being soldered.

The Helios II uses circuit boards with plated-through holes. Solder flow through to the component (front) side of the board can produce solder bridges. After soldering each group of components, clean the soldered parts immediately and then check for such bridges.

A few minutes of careful inspection at this time may prevent damage to components and hours of troubleshooting later. The best time to inspect for solder bridges is immediately after soldering; otherwise, time will be wasted going back to find the soldered areas with the possibility of overlooking or forgetting them.

To remove solder bridges, it is best to use a vacuum "solder puller" if one is available. If not, the bridge can be reheated with the iron and the excess solder "pulled" with the tip along the printed circuit traces until the lump of solder becomes thin enough to break the bridge. Braid-type solder remover, which causes the solder to "wick up" away from the joint when applied to melted solder, may also be used.

9. The Helios II circuit boards have integral solder masks (lacquer coating); masks shield selected areas on the boards and minimize the chances of creating solder bridges during assembly. Do not put masking tape over the traces. When the masking tape is removed, it can tear off the solder mask.

#### SOLDER CLEANING INSTRUCTIONS

- A. Select the following materials:

- a. Solder flux remover (kester).

- b. Flux (Acid) Brush (Cut off bristles of a tooth brush to 3/8 inch to make a cleaning brush).

- c. Paper towels (small Kimwipes are recommended).

- B. Put flux remover on the area to be cleaned and scrub the area with the cleaning brush.

- C. Put the paper towel over the scrubbed area.

- D. Brush the back side of the paper towel.

- E. Lift off paper towel and discard.

- 3.3 MODIFYING PCBs

#### 3.3.1 TOOLS AND MATERIALS REQUIRED

- 1. Exacto knife.

- 2. Soldering iron and solder.

- 3. #24 insulated, solid jumper wire.

- 4. Magnifying glass.

# 3.3.2 LOCATING IC PINS

- 1. Orient the PCB as in section 3.2.1, Orientation of PCBs.

- 2. Put your finger on pin-1 of the device called for in the instructions; for example, U23-14 (IC 23, pin-14).

- Keeping your finger at the place, flip the PCB over by twisting your wrist horizontally so that the trace side faces up and the Rev level of the board is in normal reading position.

- Note to which pin lead or pad your finger is pointing at on the other side of the PCB. Pin-1 on the trace side is square; other pin pads are round.

- Count the pins clockwise to arrive at the pin called for by the instructions. (The pins are counted counterclockwise on the legend side.)

te prove Cabinet

Figure 3-4 Helios II Diskette Drive Cabinet, Inside Top View

3-8

# 3.3.3 TO CUT A TRACE

- 1. Make two cuts between 1/32 and 1/16 inch apart.

- Lift up the trace between the cuts with an exacto knife. (Sometimes space will not permit this.)

- Inspect with a magnifying glass to be sure all copper has been removed.

NOTE

All trace cuts are to be made on the trace side of the PCB unless otherwise specified.

3.3.4 TO INSTALL A SOLDER BRIDGE

To solder a solder bridge onto a trace, first scrape off the solder mask so that the solder will adhere.

- 3.3.5 CHECK AFTER MODS

- 1. After you have soldered a connection, clean and inspect for solder bridges.

- 2. Check the modifications made by reversing the procedure in "Locating IC Pins;" that is, orient the PCB with the trace side up (where the mods are usually made); then put your finger on the connection; count the pin number, flip the PCB over and verify the device designation.

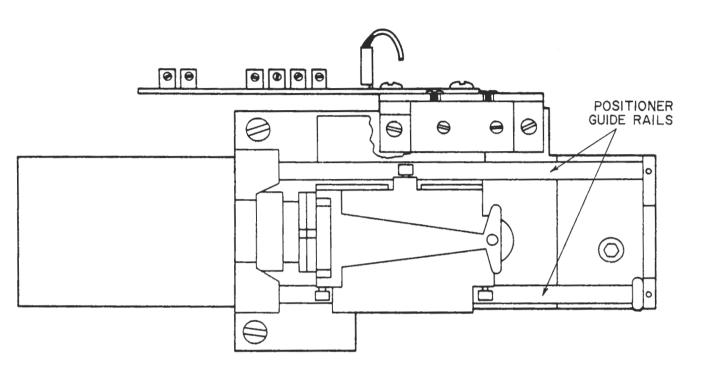

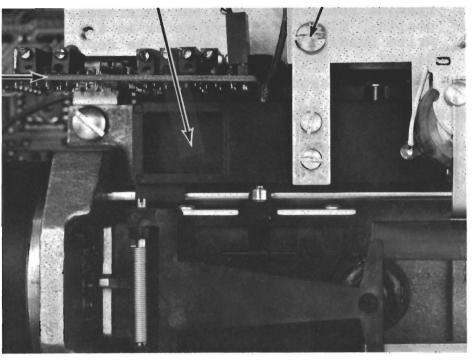

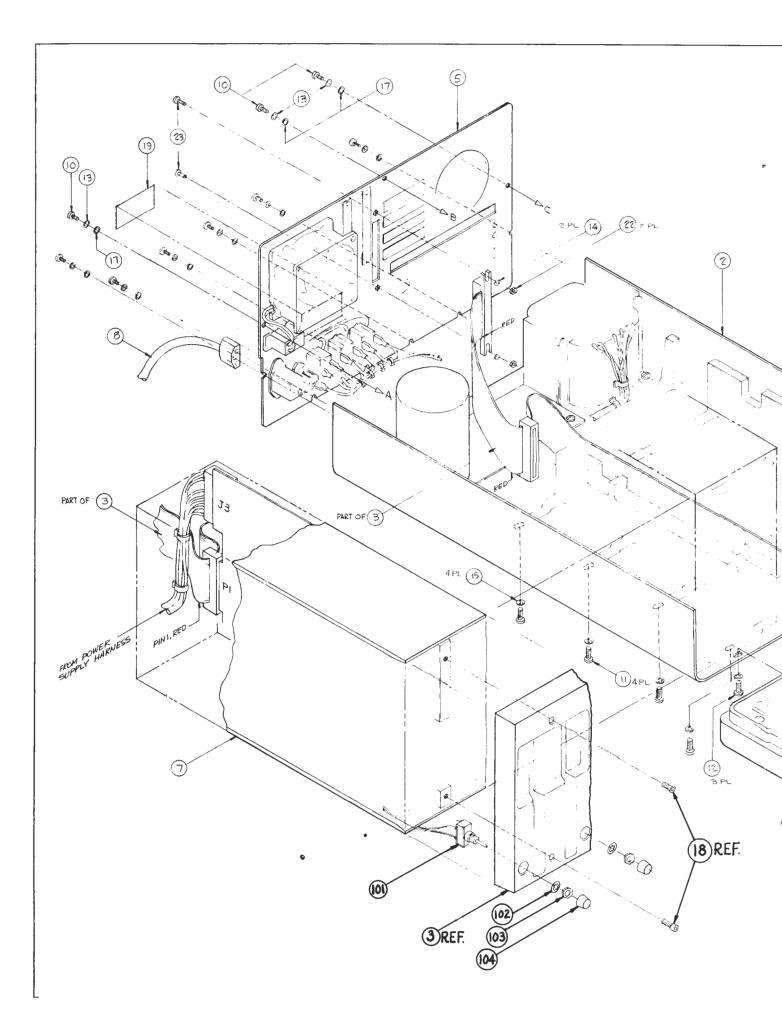

# 3.4 RE-INSTALLING THE DISKETTE DRIVE ASSEMBLY

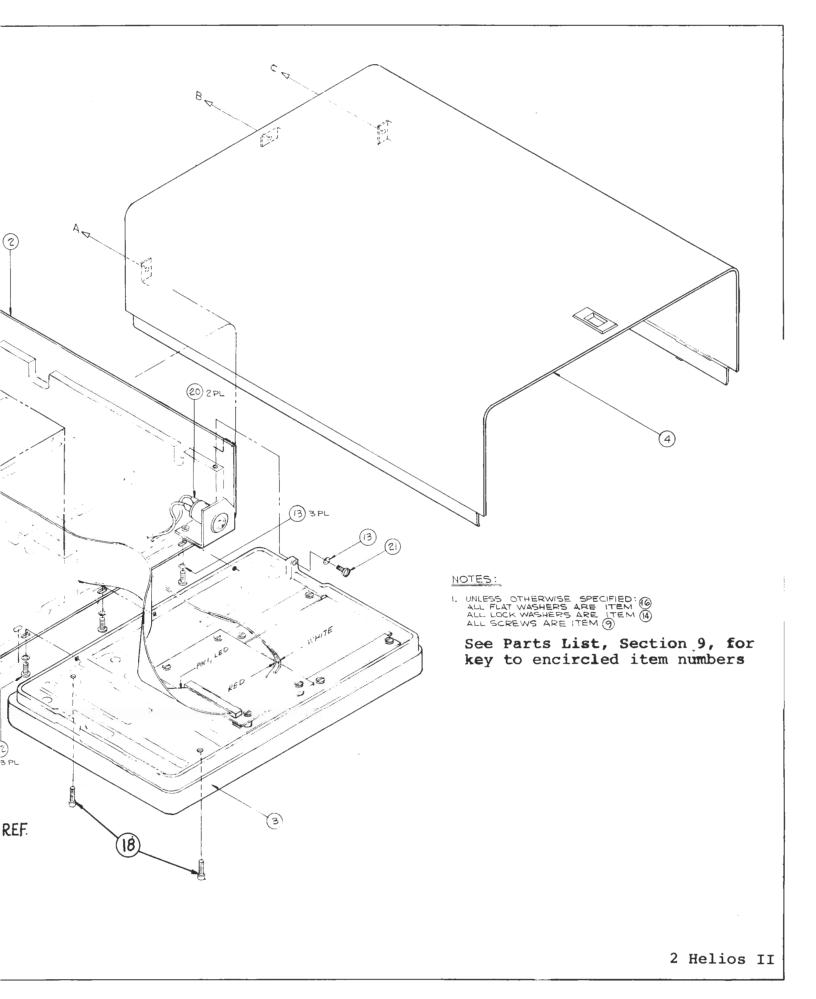

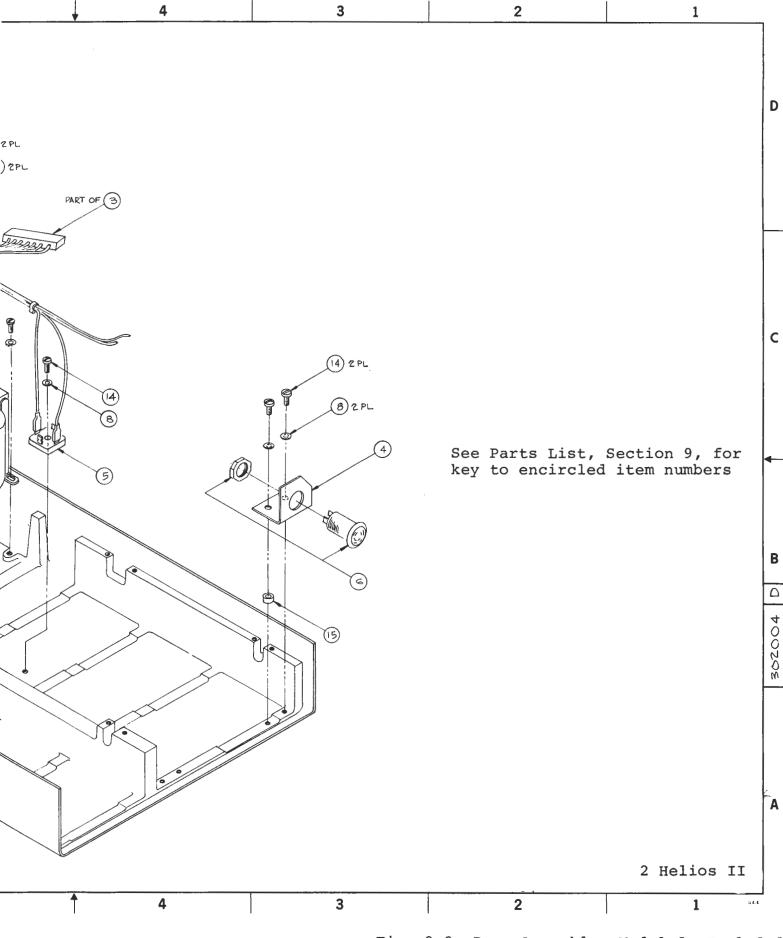

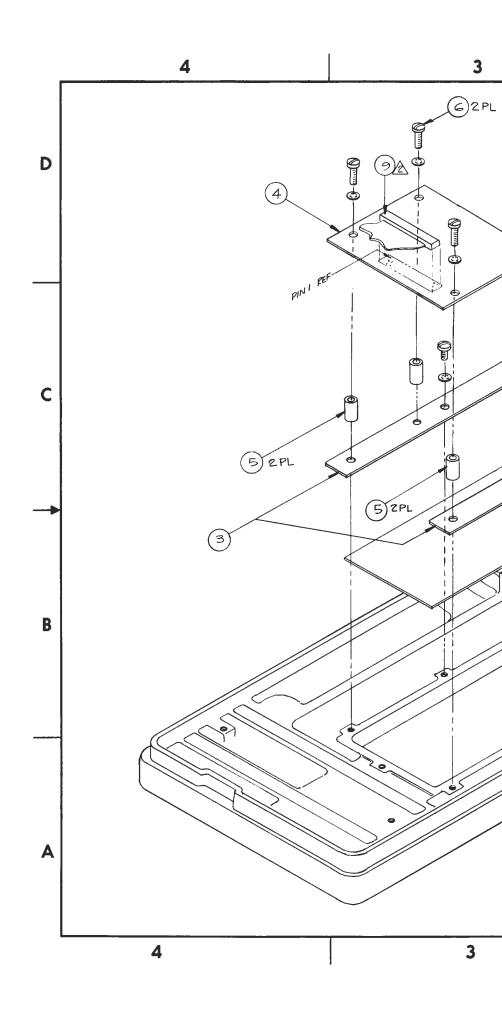

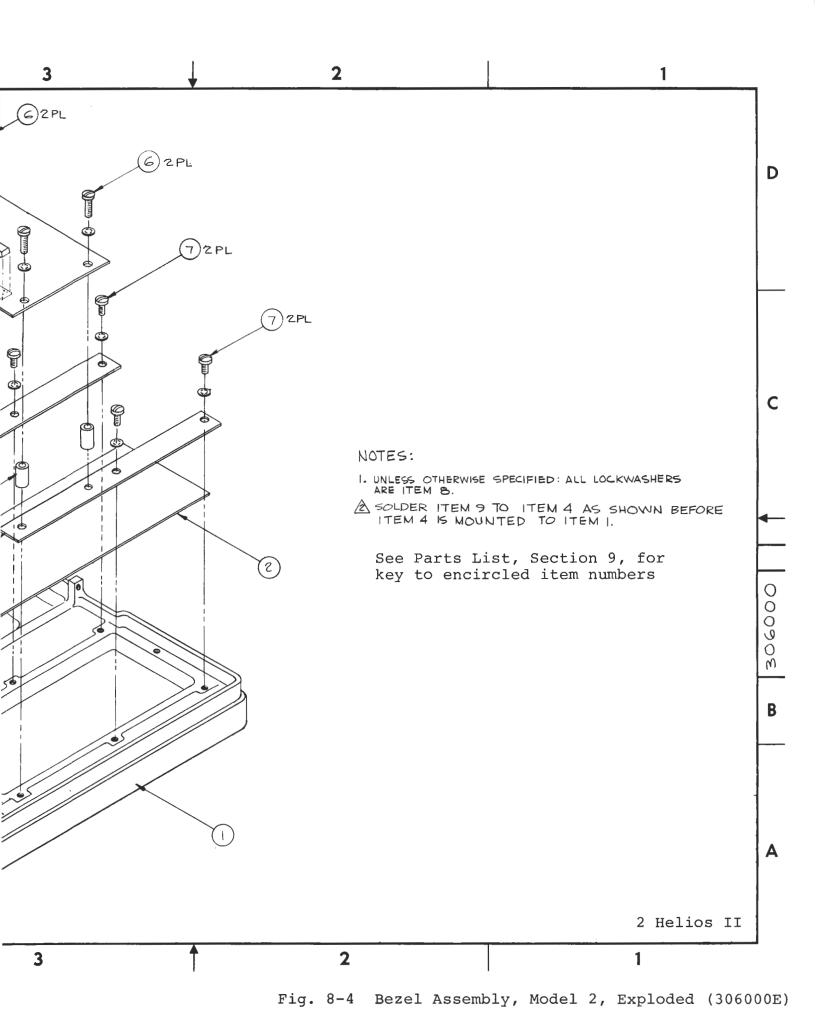

(Refer to the exploded views of the cabinet, base, and bezel assemblies, Figures 8-2, 8-3, and 8-4, respectively.)

1. Choose a clean and uncluttered area to install the drive assembly. Optical and mechanical systems within the disk drive unit are particularly susceptible to dust and dirt accumulating especially when the top cover is removed; the working area should be thoroughly cleaned and kept clean while the drive is being installed.

#### CAUTION

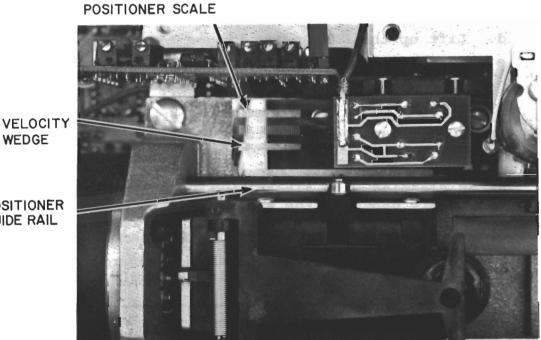

Avoid handling the drive unit by its inner components; pick it up by its outer chassis only. Alignment of these components is critical. Do not touch them unnecessarily with the hand or tools. This is especially the case with the positioner mechanism.

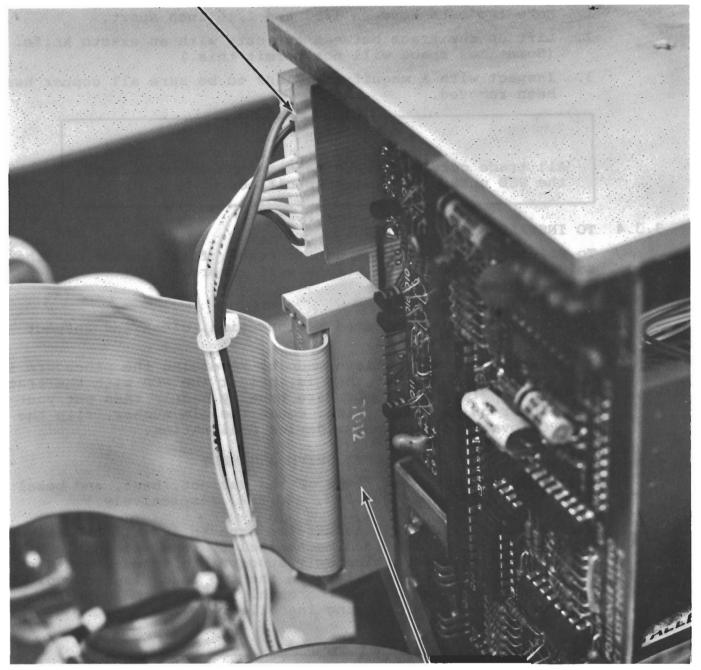

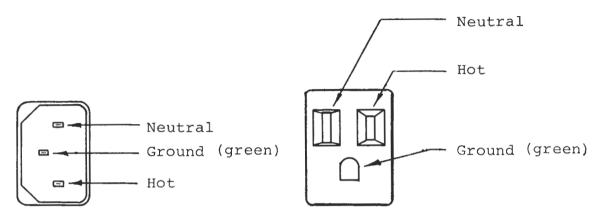

PI CONNECTOR

Fig. 3-5. Disk Drive DC Power and Signal Connectors

3-10

- Select the Helios II bezel assembly and install the disk drive to bezel using two 8-32 x l inch cap screws. Do not tighten at this time.

- 3. Reinstall the pushbutton switches on the bezel as follows:

- a. Insert switch into hole provided on bezel.

- b. Attach and tighten the internal tooth lockwashers and hexnuts over the stems of the switches.

- c. Push-back-on the pushbutton covers.

- 4. Mount the drive assembly to the base assembly using four 8 x 32 x 5/8 inch screws, four #8 internal lockwashers; tighten the screws

- 5. Make sure the #8 cap screws (step 2) are still untightened at this time.

- Attaching Bezel to Base (Refer to Fig. 8-2, Cabinet Assembly, Exploded.)

- a. Install three  $6-32 \times 7/16$  inch screws and three #6 internal lockwashers from the bottom of the base into the bezel.

- b. Install one  $6-32 \times 1/2$  inch screw and one internal lockwasher on the keyswitch side of the bezel into the base.

- c. Now tighten the two #8 cap screws which attach the bezel assembly to the drive assembly (installed in step 2).

- 7. Ensure that all screws are tight.

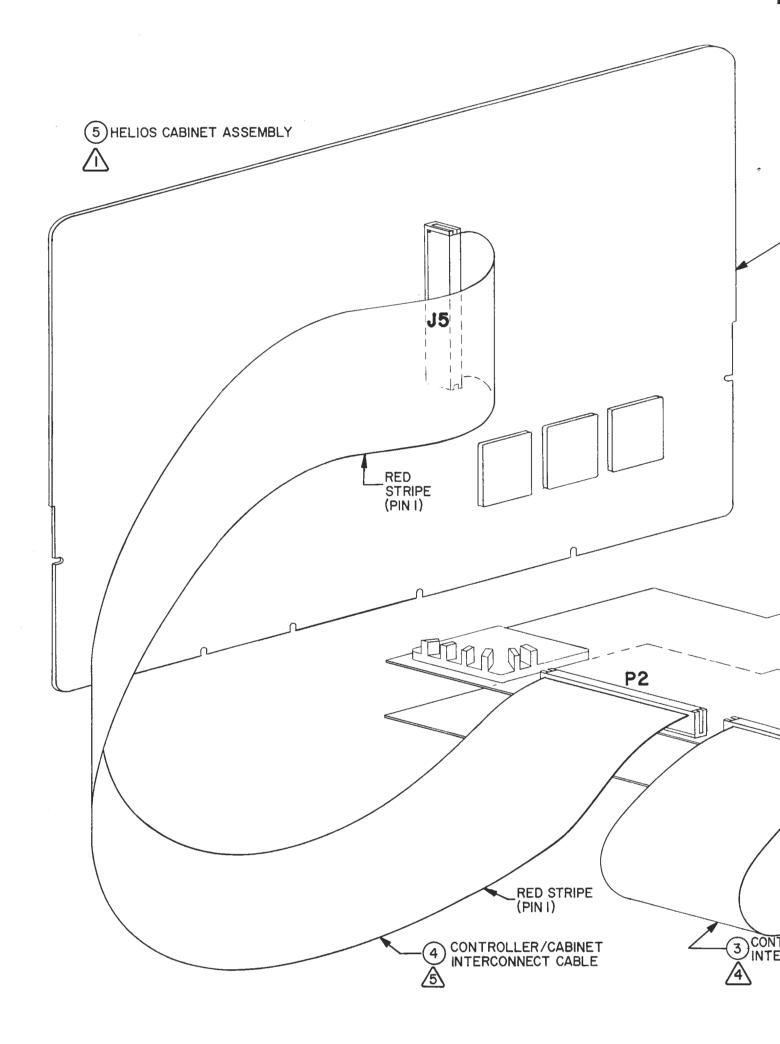

- 8. Connect the 10-pin plug connector from the power supply wiring harness to J3 of the rear of the disk drive unit. One of the pins is removed from J3 and a polarizing plug is inserted in the mating plug hole so that 10-pin plug connector can go on only one way. (See Fig. 3-5, Diskette Drive DC Power and Signal Connectors.)

- 9. Connect the flat 50-conductor signal cable (Signal/Indicator Panel Cable Assembly) from the indicator panel PCB to the disk drive at Pl. Pl is an edge connector on the PCB\* protruding its short edge at the rear of the drive assembly. The pin-l end of the plug connector (indicated by the colored stripe on the pin-l edge of the cable) goes on at the bottom of the mating PCB edge connector Pl. Pin-2 is designated on the PCB legend at this end and pin-50 on the opposite end. (See Fig. 3-5, Disk Drive DC Power and Signal Connectors.)

\*Data and Interface PCB.

10. Install the top cover on the drive cabinet. Using three  $6 \ge 32 \ge 1/4$  inch screws, attach the rear panel to the cover.

#### 3.5 OPTIONAL DC POWER FOR FORMATTER PCB

The formatter PCB receives only DC power through the S-100 edge-connector. Instead of plugging the formatter into a S-100 backplane connector, when the connector would otherwise be useful, power may be supplied through P2. The connector, J2, which mates with P2 is specified in Section 2, Specifications.\* It is not supplied in Helios II system.

To supply power through P2:

- 1. Apply +8 volts on pin 3 (center pin).

- 2. Ground on pins 1 and/or 5.

Since the voltages are arranged symmetrically around the center pin, the plug is non-polarized. The jack which mates with P2 may be oriented either way.

# CONTENTS

# SECTION 4 OPERATING INSTRUCTIONS

| SECTION |                                           |   |   |   |   |   | PAGE |

|---------|-------------------------------------------|---|---|---|---|---|------|

| 4.0     | INTRODUCTION                              | • | • | • | • | • | 4-1  |

| 4.1     | SYSTEM REQUIREMENTS                       | • | • | • | • | • | 4-1  |

| 4.2     | TERMINOLOGY, NUMBERING, AND CONFIGURATION | • | • | • | • | • | 4-2  |

|         | 4.2.1 Helios Terms                        | • | • | • |   | • | 4-2  |

|         | 4.2.2 Multi-Drive System Configuration.   | • | • | • | • | • | 4-3  |

|         | A. Terminator Resistor Pack               | • | • | • | • | • | 4-3  |

|         | B. Selector DIP                           | • | • | • | • | • | 4-3  |

| 4.3     | CARE AND USE OF DISKETTES                 | • | • | • | • | • | 4-4  |

|         | 4.3.1 Preliminary Handling Tips           | • | • | • | • | • | 4-4  |

|         | 4.3.2 Loading and Unloading The Diskette  | • | • | • | • | • | 4-4  |

|         | 4.3.3 Write Protection                    | • | • | • | • | • | 4-7  |

|         | 4.3.4 Compatibility with Other Systems.   | • | • | • | • | • | 4-8  |

| 4.4     | SETUP AND INSTALLATION                    | • | • | • | • | • | 4-9  |

|         | 4.4.1 Connecting The Cables               | • | • | • | • | • | 4-10 |

| 4.5     | INDICATORS                                | • | • | • | • | • | 4-13 |

| 4.6     | CONTROLS                                  | • | • | • | • | • | 4-14 |

| 4.7     | OPERATING INSTRUCTIONS                    |   |   |   |   |   | 4-14 |

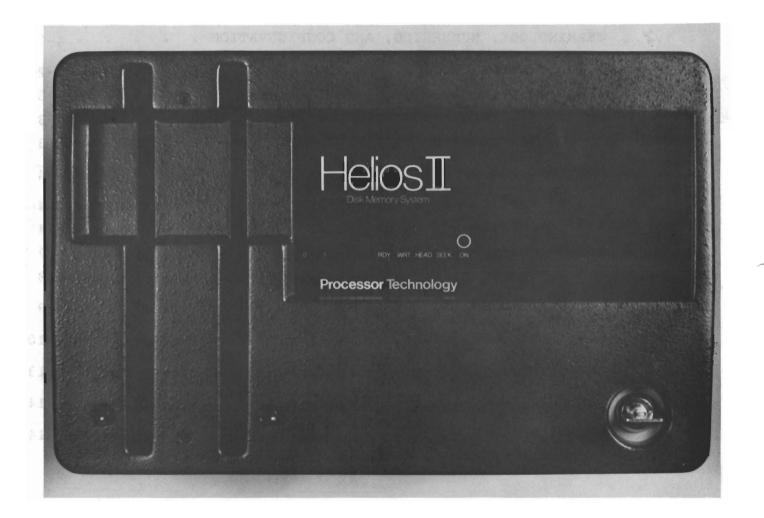

# Fig. 4-1 Helios II Front Panel

#### 4.0 INTRODUCTION

The Helios II should not be loaded with the PTDOS program until the Disk System Test in Section 5, "Testing and Trouble-shooting" is performed; however, this entire section should be <u>read</u> before performing the tests in Section 5.

This section builds up to the actual operating instructions rather than jumping into them. The operator must be adequately prepared with information and understand the relative importance of the elements in the system. For example, the care and handling of the diskette is critical in a floppy disk system. Special terminology used in this system must be defined. The sequence of steps is often as important as the steps themselves. Please read each section in the sequence given. Of course, when you become familiar with the content, the sections can be referenced as needed.

These instructions are aimed primarily at the operation of the system hardware with some references to disk operating system. Instructions for the software are in the PTDOS User's Guide, also contained in this binder.

### 4.1 SYSTEM REQUIREMENTS

- 1. Helios II tested as per Section 5, Testing and Troubleshooting.

- 2. Host computer (S-100 bus compatible), preferably a Sol-20.\*

- 3. 16 kilobytes of RAM memory (minimum) configured as follows:

4K: ØØØØH to 3FFFH

# 12K: 9ØØØH to BFFFH

- Video monitor or black and white TV converted for video input. (For TV conversion instructions, see <u>Sol Systems</u> <u>Manual</u>, Appendices, or VDM-1 Video Display Module Assembly and Test Instructions (PTC).

- 5. PTDOS program on diskette; a blank diskette.

- 6. Disk System Test (cassette).

- 7. BOOTLOAD program in either of three forms:

- a. P.T. BOOTLOAD Personality Module.

- BOOTLOAD as recorded on the front of the Disk System Test cassette (item 6 above). This requires a Sol or a host computer with CUTS interface and CUTER monitor.

- c. BOOTLOAD listing. (Refer to PTDOS User's Guide, Section 8, Appendix B, "Getting Started with PTDOS.")

- 8. <u>Helios II Disk Memory System Manual</u>, including the PTDOS User's Guide.

This section is oriented primarily with the assumption that the Helios is associated with a Processor Technology Sol system.

#### 4.2 TERMINOLOGY, NUMBERING, AND CONFIGURATION

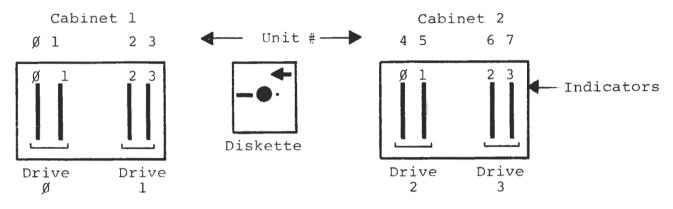

The terms used in this manual in relation to the drive configurations are illustrated in Figure 4-2 "Helios System Terminology."

Figure 4-2 Helios System Terminology

(Model 2 contains only drive  $\emptyset$ , units  $\emptyset$  and 1. See 4.2.2, Multi-Drive System Configuration.)

4.2.1 HELIOS TERMS (Refer to Fig. 4-2)

CABINET The enclosure containing one or two dual drives.

- DRIVE The dual drive assembly; containing 2 slots to accept diskettes.