This manual is developed for the exclusive use of technicians authorized to service the product(s) printed on the cover.

Due to legal requirements, no portion of the SERVICE DATA MANUAL can be reproduced or distributed without prior written approval from Heath Company.

Service Publications and Training Benton Harbor, MI 49022

© copyright August 1982

## This Document was scanned and contributed by:

## Barry A. Watzman

- INTRODUCTION

- 2. SYSTEM

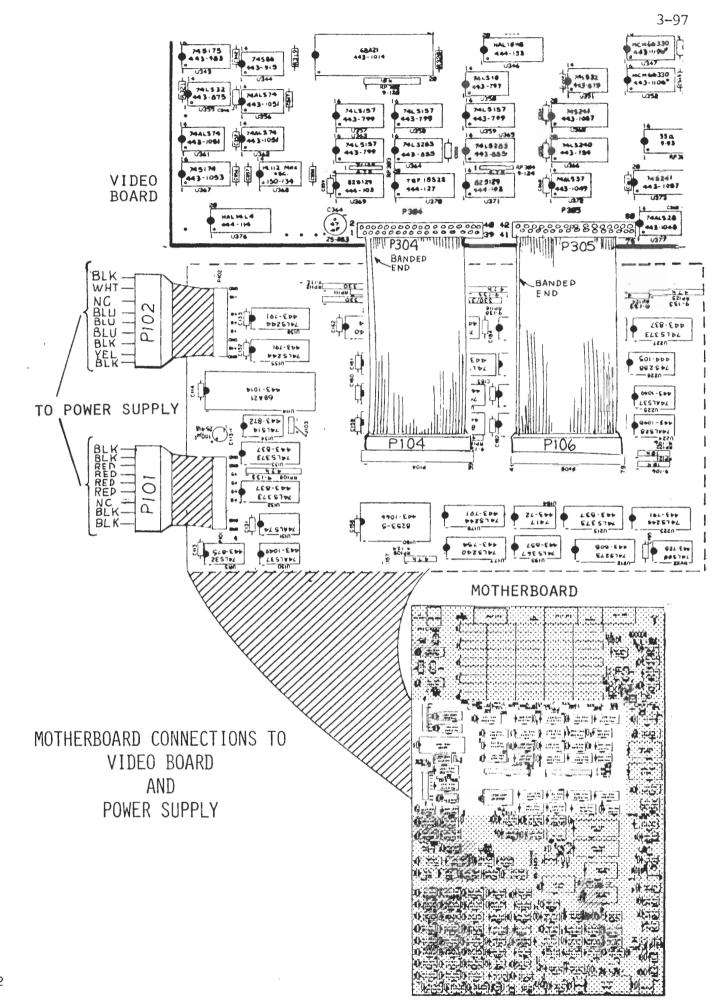

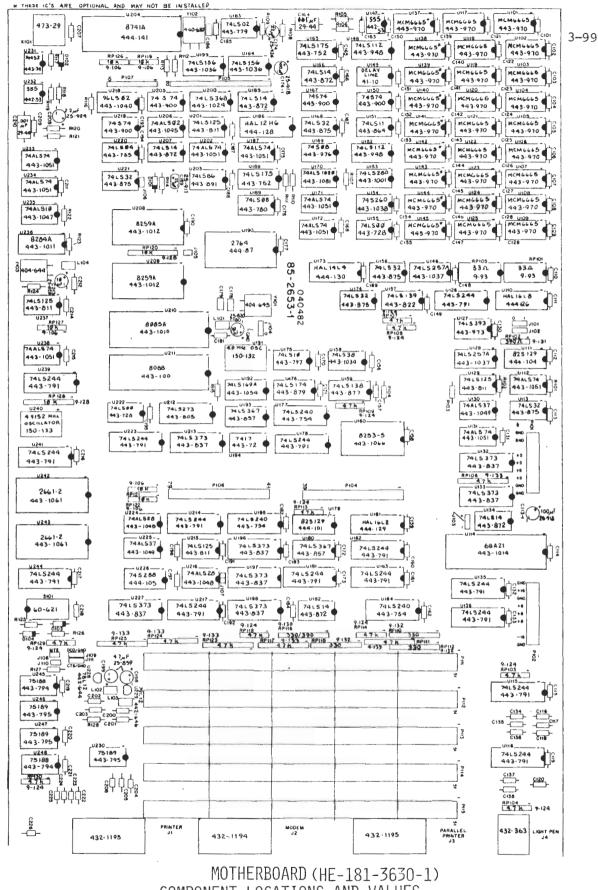

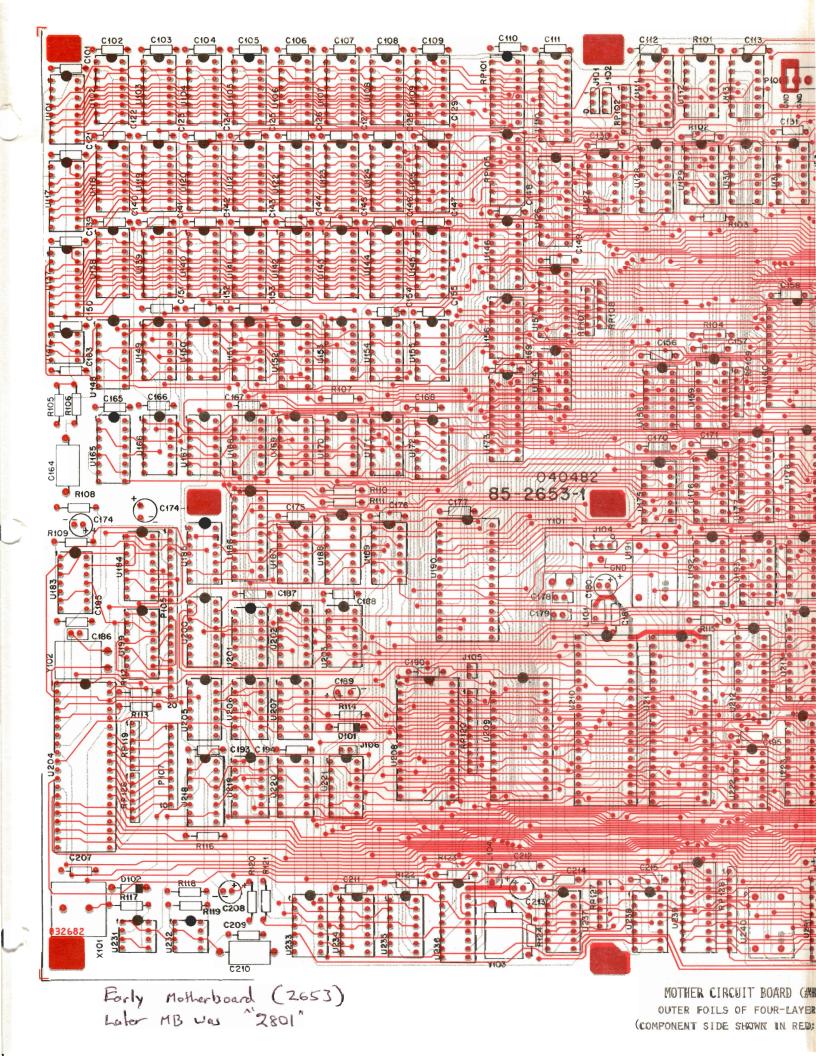

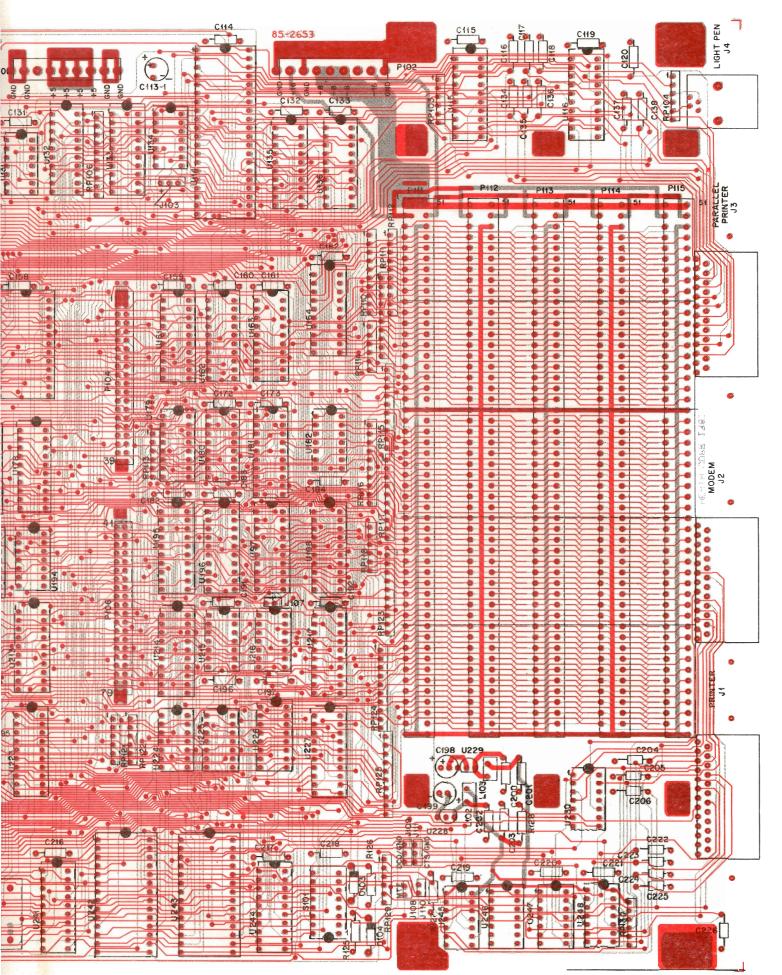

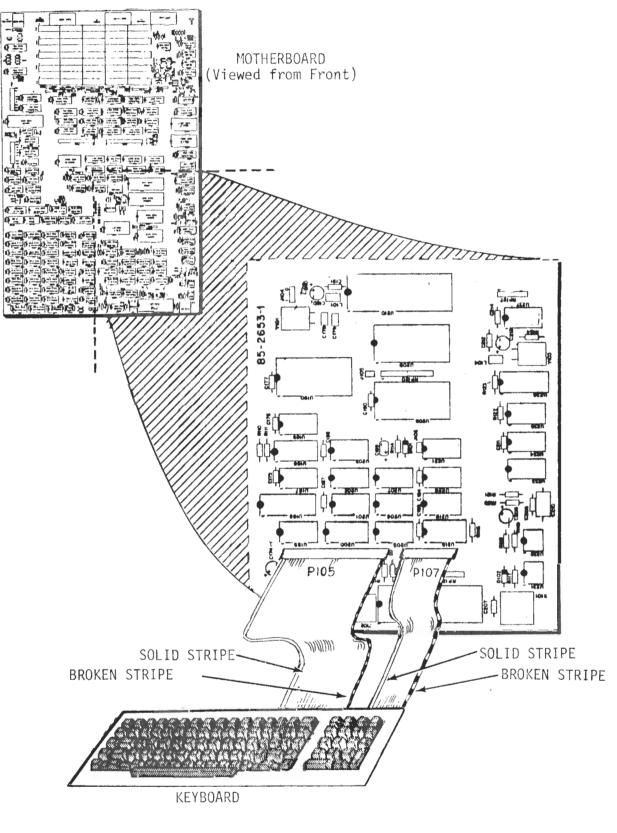

- **3.** MOTHERBOARD

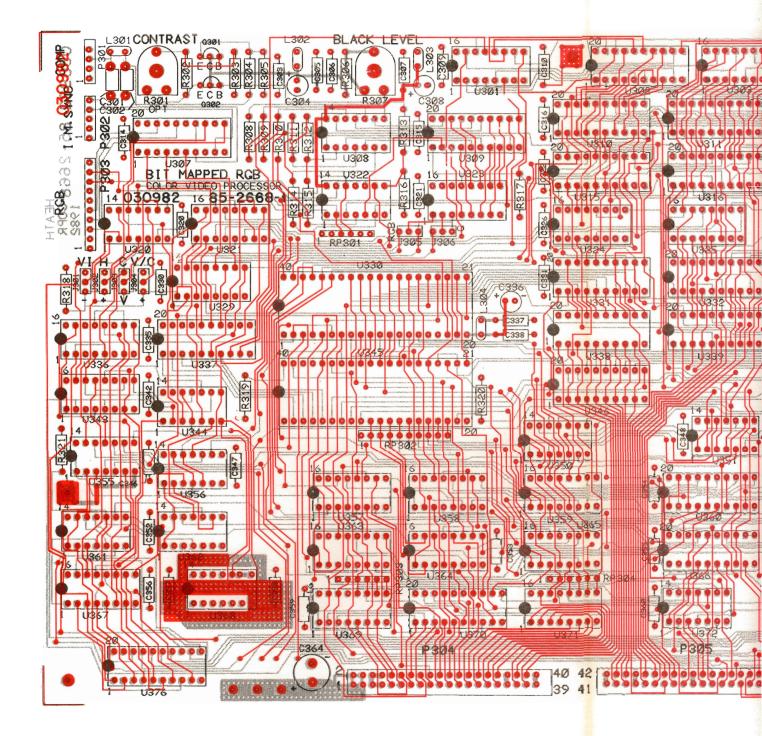

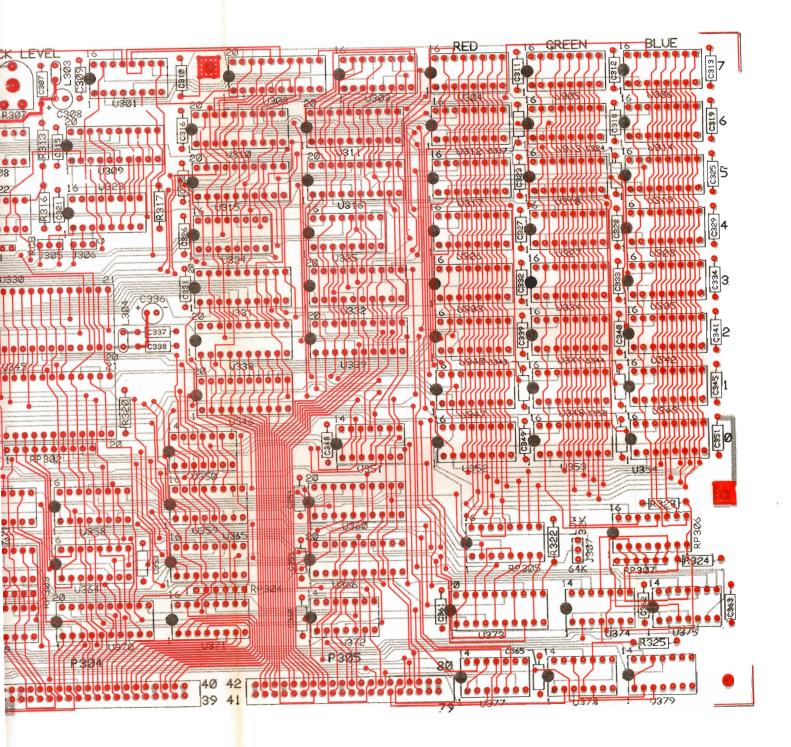

- 4. VIDEO BOARD

- 5. DISK CONTROLLER AND DRIVES

- 6. VIDEO MONITOR

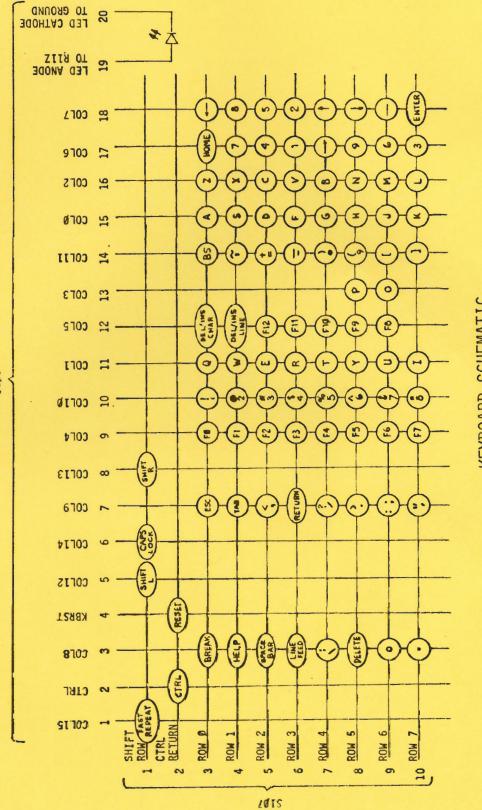

- 7. KEYBOARD

- 8. POWER SUPPLY

- 9. ACCESSORIES

- **10.** SERVICE BULLETINS

- . DATA SHEETS

- 12. APPENDICES

- 13. DIAGNOSTICS

The H/Z-100 COMPUTER SERVICE DATA MANUAL (Blue Book) contains in-depth data about the new H/Z-100 Computers, both the All-In-One model and the Low-Profile model.

The information in this manual will help you efficiently troubleshoot and repair H/Z-100 Computers to either the module level or the component level.

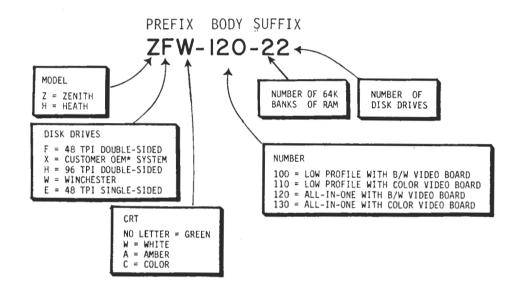

There are thirteen sections in this manual. The first is a general introduction to the manual and an explanation of the model numbering system.

Section 2 introduces you to the Computer System and is presented in the familiar Blue Book format.

The following six sections, also laid out in the Blue Book format, contain detailed data on the:

Motherboard,

Video Board,

Disk Controller and Drives,

Video Monitor,

Keyboard, and

Power Supply

The balance of the manual is set aside for your inclusion of material for Accessories, Service Bulletins, Data Sheets, and Diagnostics. Data on the S-100 bus has already been included in an Appendice section.

All thirteen sections are contained in an easy-to-use 3-ring binder...this will let you insert updates and new product information and will let you keep your H/Z-100 Computer Blue Book up to date.

And now for a look at the model number system ...

Each model number lets you see at a glance the main features of that particular model. The illustration below shows what each portion of the model number means:

So, if the model number is ZF-120-22, it means: 7 a Zenith wired model,

F with a 48 TPI,

W a white CRT,

-120 and it's an ALL-IN-ONE with a black and white video board -2 with two banks of 64K of RAM (2 x 64 = 128K RAM), and 2 two disk drives!

A couple of things to remember ...

Note that in the body (or number), "Color Video Board" refers to the ability of the video board to produce color--not the nature of any CRT. Also, in the suffix portion of the model number, characters are alphanumeric for OEM models (and stand for a specific OEM); for all other models, the characters are numeric.

Carefully read each section in this Blue Book. After doing so, you'll not only become an expert on the H/Z-100, you will also be able to quickly locate the exact information that you need to service the unit.

Before learning how each module works in the Computer, you should know how the H/Z-100 works as a complete system. To gain this understanding, begin by reading section 2, "System."

. . . . . .

-----

.

### SYSTEM

| INTRODUCTION                     | 2-1   |

|----------------------------------|-------|

| SPECIFICATIONS                   | 2-5   |

| OPERATION                        | 2-11  |

| CONFIGURATION                    | 2-17  |

| NORMAL OPERATING CHARACTERISTICS | 2-37  |

| BLOCK DESCRIPTION                | 2-41  |

| DISASSEMBLY                      | 2-69  |

| VISUAL CHECKS                    | 2-85  |

| TROUBLESHOOTING                  | 2-93  |

| PARTS LISTS                      | 2-119 |

The H/Z-100 is a versatile computer system. This computer is designed to be compatible with existing hardware and software products. The H/Z-100 offers an industry standard bus, a widely accepted operating system, high-resolution graphics, expandability, and high-speed computing to the prospective customer.

The computing functions of the H/Z-100 are controlled by two microprocessors; an 8088 and an 8085. The 8088 processor features 16-bit processing in an 8-bit environment. This gives the computer 16-bit speed and power, while still retaining an 8-bit bus. The 8085 processor is an 8-bit processor that is 8080 code compatible. This processor assures a large available software base. Thus, the computer buff with existing 8-bit software is supported.

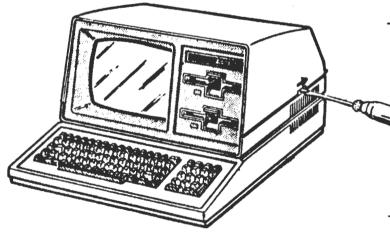

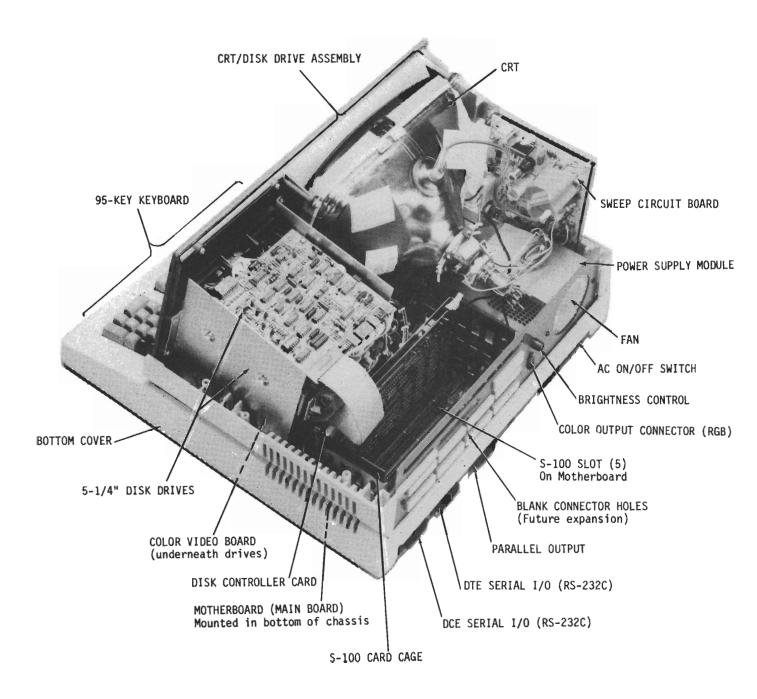

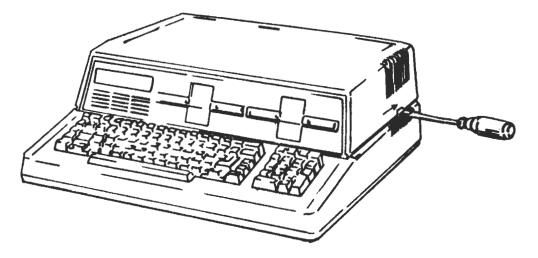

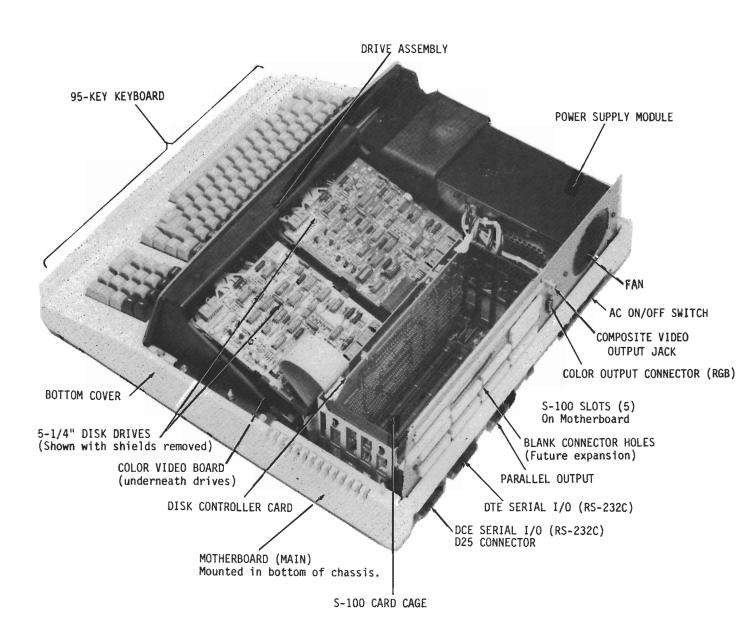

The H/Z-100 computer is available in two models; the All-in-One and the Low Profile. The main difference between the two models is that the All-in-One contains a built-in video monitor, while the Low Profile does not. Both models include a mass-storage device, two processors, Dynamic RAM, and a professional keyboard.

Flexibility of the computer is assured by a 5-slot, S-100 compatible bus. The S-100 bus was designed to conform to the IEEE-696 definition of the S-100 bus. This definition was chosen since it is the widely accepted standard among computer manufacturers. This bus design provides an opportunity for the user to tailor a hardware environment to suit his needs. Additional I/O, slave processors, and special function S-100 boards from Heath Company and other sources will work within the H/Z-100.

To communicate with the outside world, the H/Z-100 motherboard contains on-board peripheral connections. These connections consist of two serial ports and a parallel port. The serial ports are configured to RS-232C standards. One is a DCE interface and the other is a DTE interface. The parallel port is configured as a Centronics compatable printer interface. Because these connections are built into the motherboard, a separate S-100 I/O card is not needed. Thus, space in the S-100 card cage is conserved.

In addition, the H/Z-100 contains many other features. These include:

- Two keyboard modes.

- Light pen input.

- Three timer outputs.

- H-19 graphic and escape code compatible.

- Wired and tested mother board.

These features, along with the stylish molded cabinet, make the H/Z-100 computer a powerful computing tool.

The information in this section of the manual enables you to service the H/Z-100 to the module level. If you require more information on an individual board, refer to the section entitled by the board name.

٤

## SPECIFICATIONS 2-7 CPU 2-7 VIDEO DISPLAY 2-8 BUS STRUCTURE 2-8 TIMER 2-8 **KEYBOARD** DISK CONTROLLER 2-9 INPUT/OUTPUT 2-9 2-10 POWER SUPPLY TEMPERATURE AND HUMIDITY 2-10 2-10 DIMENSIONS 2-10 WEIGHT 4

### CPU

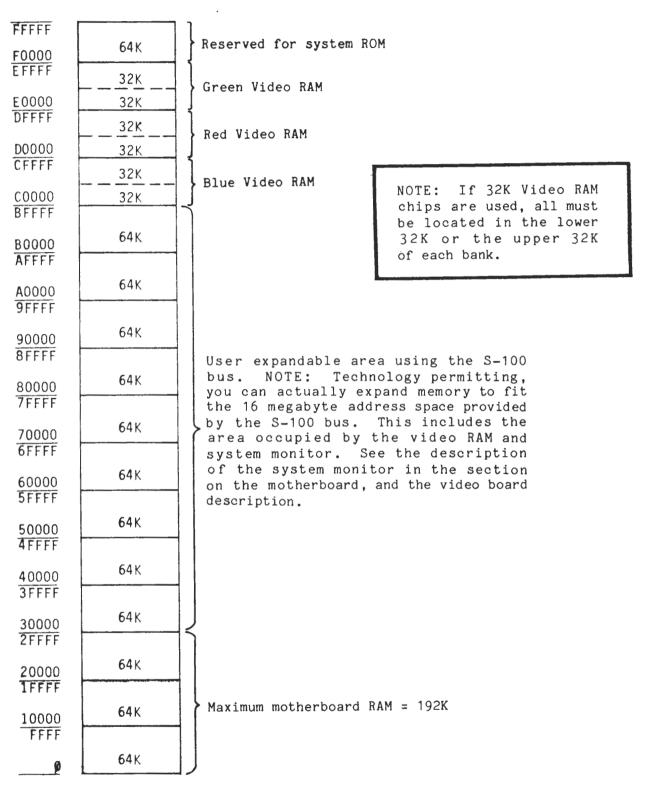

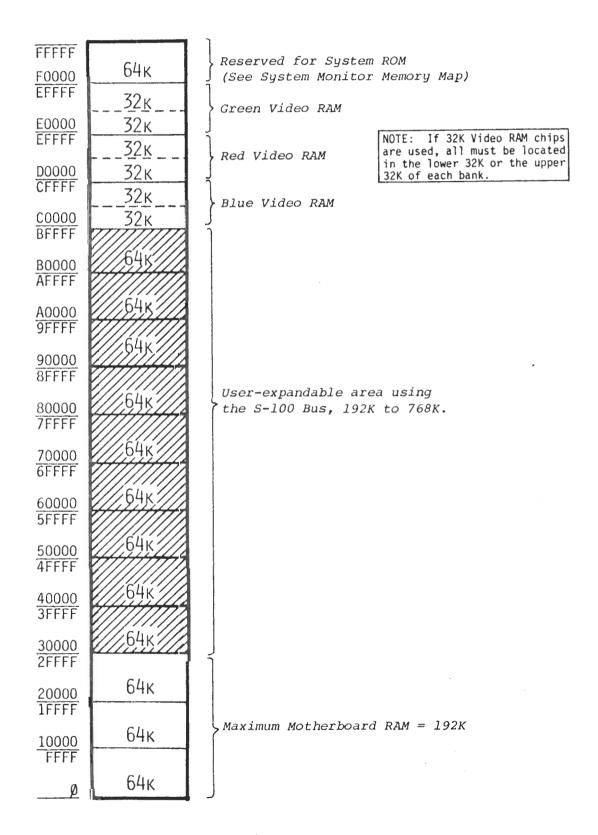

Processor 1 ..... Intel 8088. Clock ..... 5 MHz. Type ..... 16-bit CPU. Wait State ..... Memory, Ø; I/O, 1. Processor 2 ..... Intel 8085. Clock ..... 5 MHz. Type ..... 8-bit CPU. Wait State ..... Memory, 1; I/O, 2. On-Board Memory ..... 64K to 192K bytes in 64K increments. Parity checked. Memory Space ..... 1 megabyte. Monitor Space ..... One 64K page. Video RAM Space ..... Three 64K pages. User Memory Space ..... 3/4 megabyte. Interrupts Controller ..... Dual 8259A. System ...... 15-level priority vector interrupt.

### VIDEO DISPLAY

| CRT (All-in-One)  | 12" diagonal, green non-glare<br>or optional white or amber.                                                                                    |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Display Format    | 25 lines of 80 characters.                                                                                                                      |

| Display Size      | 6.5" high x 8.5" wide.                                                                                                                          |

| Character Size    | 0.2" high x .1" wide (approximate).                                                                                                             |

| Character Set     | "Soft", dynamically redefinable.                                                                                                                |

| Character Type    | 5 x 9 dot matrix.                                                                                                                               |

| Dot Resolution    | 640 x 225 pixels.                                                                                                                               |

| Colors (optional) | Eight: Red, green, blue, white,                                                                                                                 |

| Gray Scale        | black, cyan, magenta, and yellow.<br>Eight levels when a monochrome<br>display is used and the color<br>option is installed in the<br>computer. |

```

Options

Interlace Mode ...... 640 x 500 pixels.

Pages ..... Second page of display.

Light Pen ..... One pixel resolution.

Outputs ..... Red, green, blue, composite video,

composite sync and separated

horizontal and vertical sync.

```

### BUS STRUCTURE

Type ..... Proposed IEEE-696 (S-100). Number of Slots ..... Five. Data Bus Width ..... Eight bits. Address Bus Width ..... Twenty-four bits. I/O Addressing ..... Eight bits.

### TIMER

Type ..... Programmable.

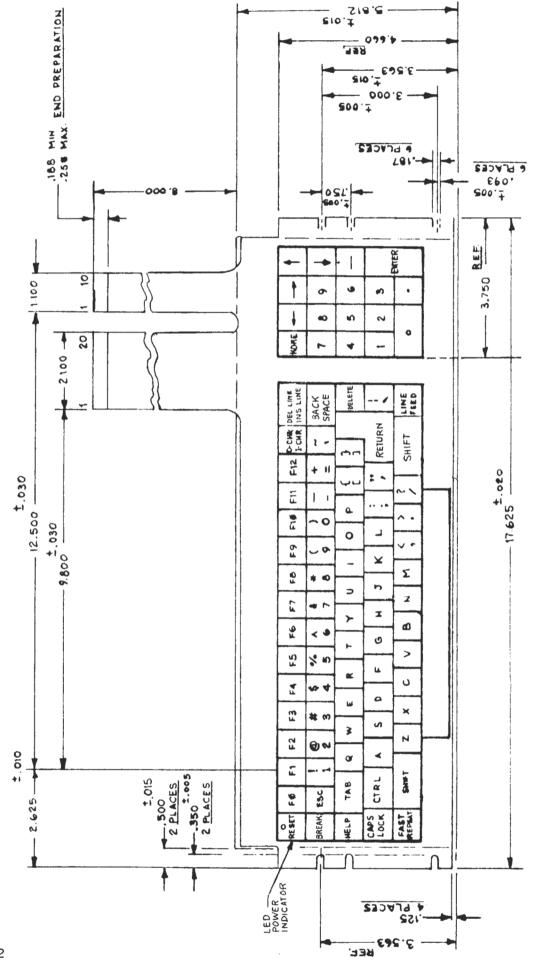

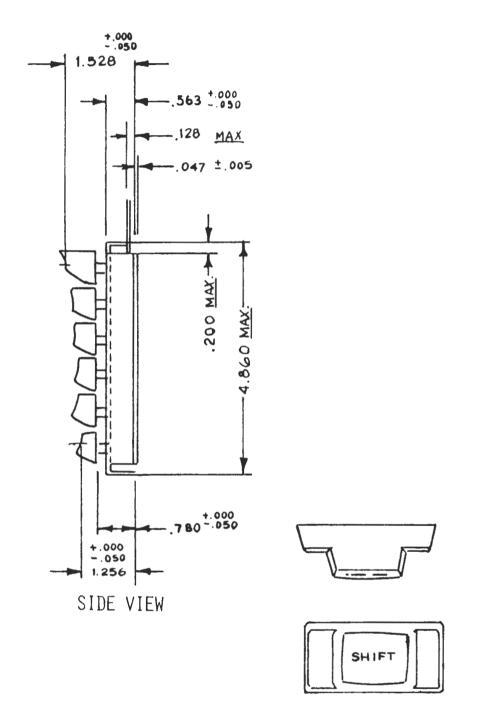

### **KEYBOARD**

| Туре      | 95 keys: 61-key alphanumeric    |

|-----------|---------------------------------|

|           | and 16-key function and control |

|           | section, plus an 18-key numeric |

|           | and cursor control section.     |

| Modes     | Two: ASCII and Event Driven.    |

| Processor | FIFO buffer (17 character).     |

| Key Click | May be disabled.                |

DISK CONTROLLER (May be omitted on S-100 Card) Type ..... WD1797. Drives Supported ..... Up to four each. 5-1/4" ..... Single/double-sided, 48 TPI, single/double density. 8" ..... Single/double-sided, single/ double density. Data Separator ..... Phase-locked loop. Precompensation ...... Variable independently for both 5-1/4" and 8" sizes. Data Transfer ..... Programmed using wait states, interrupt or polling. Internal Disk Drive Size ..... 5-1/4". Sides ..... Single or double. Tracks per Inch ..... 48. Capacity (formatted) .. 80K, 160K, or 320K; depending on the number of sides and density. Track Format ..... 4K, eight sectors of 512 bytes each. Stepping Speed ...... 6 milliseconds per track or faster. External Disk Drive Interface Type ..... Shugart 850 or equivalent. Winchester Disk Drive (optional) Type ..... 5" replacing one internal disk drive. INPUT/OUTPUT Serial I/O ..... Dual RS-232 ports, one DTE and one DCE. Baud Rate ..... 110 to 38,400. Operation ..... Asynchronous RS-232 or synchronous. Stop Bits ..... One, one and one half, or two. Word Length ..... Five, six, seven, or eight bits. Break Capability ..... Detection and generation. Parity ..... Even, odd, or none. Parallel I/O ..... Eight-bit output only. Type ..... Centronics.

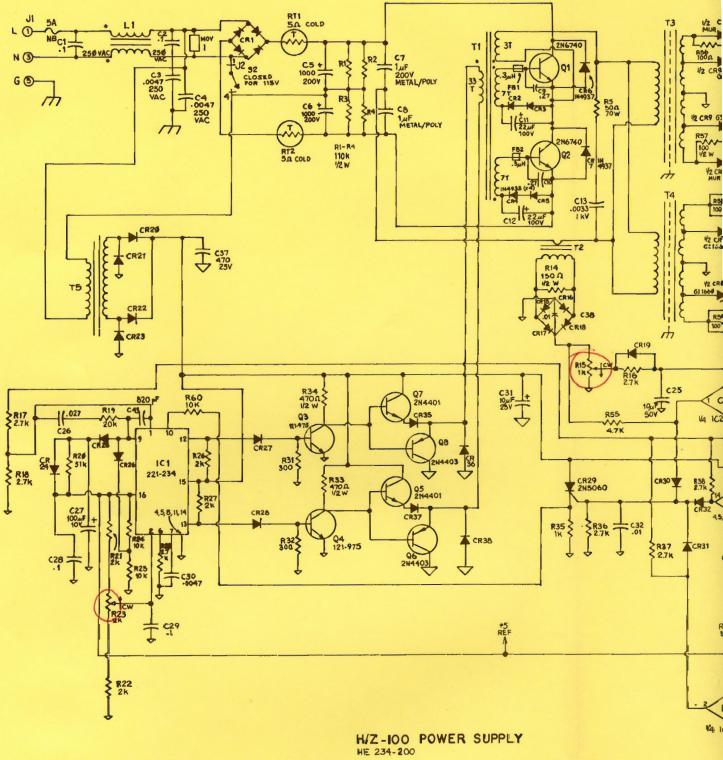

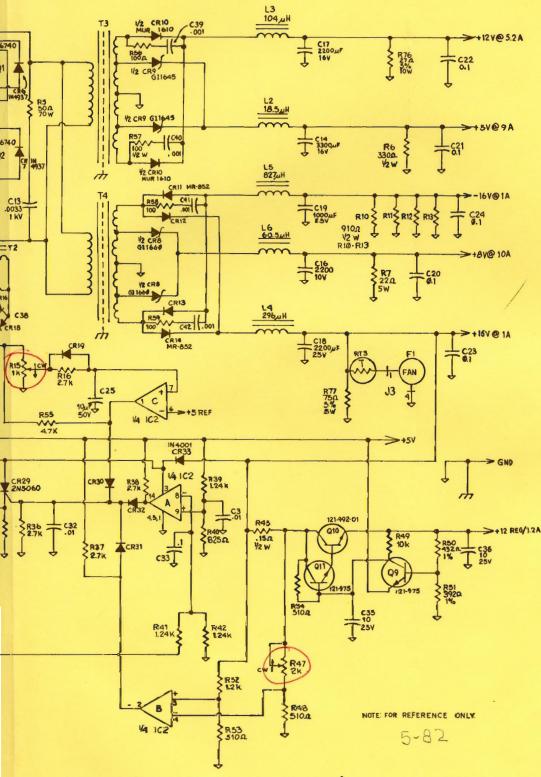

### POWER SUPPLY

Input, Volts ..... 120 VAC or 240 VAC. Input, Hertz ..... 50 Hz or 60 Hz.

### TEMPERATURE AND HUMIDITY

Operating Temperature ... 15.6 to 32.2 degrees Celsius (60 to 90 degrees Fahrenheit). Storage Temperature .... 10 to 43 degrees Celsius (50 to 110 degrees Fahrenheit). Operating Humidity ..... 8% to 80%, noncondensing.

### DIMENSIONS

| All-in-One                | 19" W x | 19.5" D | x 13.5" H  |

|---------------------------|---------|---------|------------|

|                           | (47.5 x | 48.75 x | 33.75 cm). |

| Low-Profile w/o Monitor . | 19" W x | 19.5" D | x 7.125" H |

|                           | (47.5 x | 48.75 x | 17.8 cm).  |

### WEIGHT

All-in-One ..... 50 lbs (22.7 kg). Low-Profile ..... 40 lbs (18.2 kg).

Heath Company and Zenith Data Systems reserves the right to discontinue products and to change specifications at any time without incurring obligation to incorporate new features in products previously sold.

# OPERATION 2-13 POWER-UP AND RESET 2-14 2-14 2-14 BOOT VERSION H-19 EMULATION r

In this section, operation of the H/Z-100 computer is discussed. This specifically covers power-up and reset, MTR-100 commands, and H-19 emulation. Information on hardware and peripheral applications can be found in the configuration section.

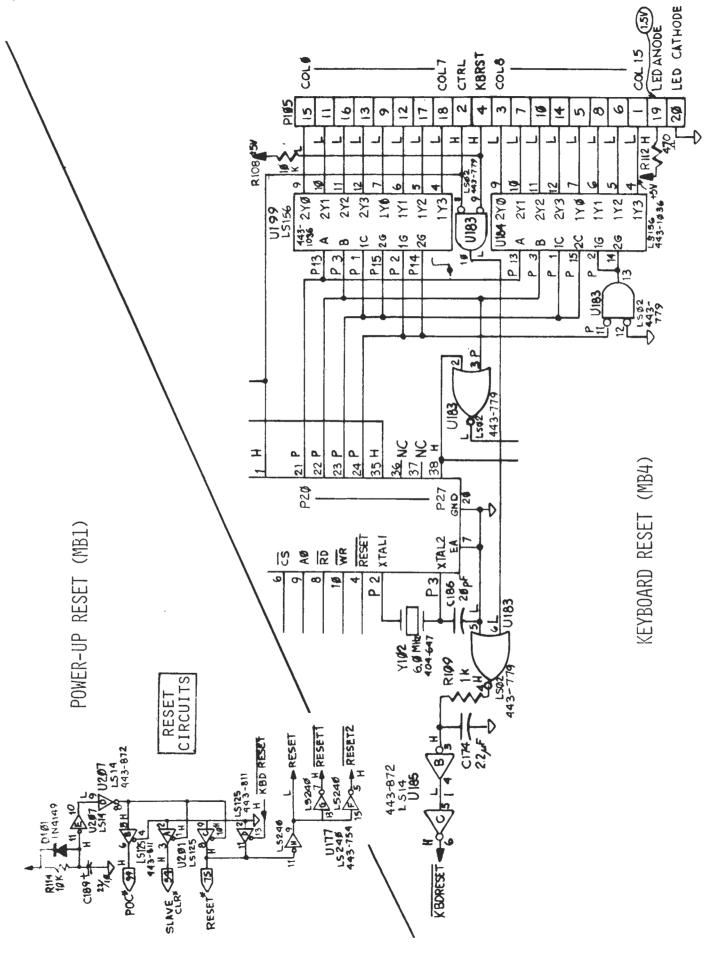

### POWER-UP AND RESET

When shipped to the customer, the H/Z-100 is hardware set by S101 in auto-boot mode. This means that upon power-up or reset, MTR-100 will initialize the computer and automatically start the boot routine. If a disk is not found in the default drive within 30 seconds after power-up or reset, MTR-100 will print a boot error message and enter the monitor mode. The boot routine, however, may be averted in two different ways. The first way is to reset S101 (this is covered in Configuration). The second way is to use the delete key. By pressing the delete key during the boot routine, the routine is halted and the computer enters the monitor mode.

To power-up the computer, flip the switch on the right rear corner of the computer. To reset, the CTRL and RESET keys are simultaneously pressed. During the initialization process, MTR-100 selects the active processor, initializes the hardware devices, sizes RAM, and sets the stack segment. MTR-100 then times out 30 seconds and starts the boot routine.

There are two MTR-100 commands; Boot and Version. MTR-100 features command completion where only the first letter of the command is typed in and the computer will finish typing in the rest of the command. A detailed description of each command follows. Please note that these commands will be ignored if the computer is not in the monitor mode.

### BOOT

The boot command will boot from the default drive specified by bits 0-2 of the configuration dip switch S101. MTR-100 contains all the code necessary to boot an operating system from the default drive. The command is initiated by pressing the B key after the hand prompt. The computer will respond with "oot". The pressing of the RETURN key will cause MTR-100 to jump to and start the boot-up routine. Pressing the DELETE or BACKSPACE keys will cause the boot routine to abort. An aborted boot returns the computer to the monitor mode, even if auto-boot is configured.

### VERSION

The version command is intended to allow non-technical users of the H/Z-100 to identify which version of MTR-100 is installed in their machine. The command is implemented by pressing the V key after the hand prompt. The computer will respond with "ersion" and MTR-100 will identify itself.

### H-19 EMULATION

To keep the H/Z-100 compatible with existing software, H-19 emulation of the keyboard and character display is necessary. This is accomplished through the use of subroutines within MTR-100. All of the H-19 escape sequences except the ANSI mode are supported. It is important to note that the H-19 escape sequences are supported during software control. Since there is no OFF LINE key, the terminal cannot be programmed directly from the keyboard. For further information on the keyboord, refer to the keyboard section of this manual. SUMMARY OF H/Z-100 ESCAPE CODES

| Escape<br>Sequence  | Definition                                               | Escape<br>Sequence        | Definition                                                   | Escape<br>Sequence        | Definition                       |

|---------------------|----------------------------------------------------------|---------------------------|--------------------------------------------------------------|---------------------------|----------------------------------|

| CURSOR FUNCTIONS    |                                                          | Configuration (continued) | tinued)                                                      | ALTERNATE KEYPAD SEQUENCE | SEQUENCE                         |

| ESC A<br>FSC B      | Cursor up<br>Cursor down                                 | ESC ×*                    | Set mode(s)<br>*                                             | ESC ?M                    | Enter key<br>Pariod ( ) kev      |

|                     | Cursor right                                             |                           | 1 = Enable 25th line                                         |                           | 0 key                            |

| ESC D               | Cursor left                                              |                           | 2 = No key click                                             |                           | 1 key                            |

| ESC H               | Cursor home                                              |                           |                                                              |                           |                                  |

| ESC I               | Reverse index                                            |                           | п                                                            |                           | 3 key                            |

| ESC Y               | Direct cursor addressing                                 |                           | 11                                                           | ESC 7t                    |                                  |

| ESC n               | Save cursor position<br>Cursor position report           |                           | o = Keypad Snifted<br>7 - Fnter alternate kevnad mode        |                           | 6 kev                            |

| ESC k               | Set cursor to previously saved                           |                           |                                                              |                           |                                  |

|                     | position                                                 |                           | 11                                                           | ESC 7x                    |                                  |

| ERASING AND EDITING | ING                                                      |                           | ; = Nonblinking cursor<br>< = Disable keyboard auto repeat   | ESC 54                    | укеу                             |

| r SC F              | Clear disnjav and home curtor                            |                           | ? = Enable key expansion                                     | ADDITIONAL FUNCTIONS      | IONS                             |

|                     | Erase to end of page                                     | ESC y*                    | Reset mode(s)                                                | ESC 7                     | Identify as VTG2(FSC /K)         |

| ESC K               | Erase to end of line                                     |                           | 1 = Disable 25th line                                        |                           | Transmit page                    |

|                     | Insert line                                              |                           |                                                              | ESC ]                     | Transmit 25th line               |

|                     | Delete line                                              |                           | u                                                            | ESC >                     | Transmit current line            |

| ESC N               | Delete chârăcter<br>Evit insert obsrecter mode           |                           | u                                                            | ESC                       | Transmit character at cursor     |

|                     | EAIC INSEL CHARACTER MODE<br>Friet Insert character mode |                           |                                                              | ESC 10                    | Zenith identify terminal type    |

|                     | Erase to beginning of display                            |                           | o ≃ Keypad unsnifted<br>7 ≂ Frit alternate kevbad mode       |                           |                                  |

| ESC 1               | Erase entire line                                        |                           |                                                              |                           | Foreground and background colors |

| ESC O               | Erase to beginning of line                               |                           |                                                              |                           | D = Black                        |

|                     | _                                                        |                           | ; = Blinking cursor                                          |                           | i 11                             |

| CONFIGURATION       |                                                          |                           | C = Enable keyboard auto repeat<br>2 - Disable key expansion |                           | #1                               |

| ESC r#              | Modify baud rate                                         | ESC z                     | Reset to power-up configuration                              |                           | 3 = Magenta<br>4 = Green         |

|                     | . *                                                      |                           |                                                              |                           |                                  |

|                     | A = 110<br>B = 150                                       | MODES OF OPERATION        |                                                              |                           | 6 = Yellow<br>7 - White          |

|                     | н                                                        | ESC F                     | Enter graphics mode                                          | ESC {                     | Keyboard enable                  |

|                     | 11                                                       | ESC G                     | Exit graphics mode                                           | ESC ]                     | Keyboard disable                 |

|                     | u                                                        |                           |                                                              | ESC V                     | Wrap-around at end of line       |

|                     | F = 1800<br>G = 2000                                     | ESC =                     | Enter alternate keypad mode                                  | ESC W                     | Discard at end of line           |

|                     | 1 11                                                     |                           | EXIC ALVERIACE KEYPAG MODE                                   |                           |                                  |

|                     | н                                                        | ESC p                     | Enter reverse video mode                                     |                           |                                  |

|                     | J = 4800 K = 7200                                        | ESC q                     | Exit reverse video mode                                      |                           |                                  |

|                     | L = 9600                                                 | ESC t                     | Enter keypad shifted mode                                    |                           |                                  |

|                     |                                                          | ESC G                     | EXIC REALED SHITCED MODE                                     |                           |                                  |

2-15

| ſ               | 10 <b>1</b> 0     |        | 6B ×               | 72 1               | 79 y               |                    |

|-----------------|-------------------|--------|--------------------|--------------------|--------------------|--------------------|

|                 | (144) [100] 64    |        | (153)   107   6B   | (162)  114   72    | (17)   121   79    |                    |

|                 | (143)  99   63 c  |        | (152) [ 106] 6A    | (161) [113] 71 q   | (170)   120   78 × |                    |

| 50L3            | (142)   98   62 b |        | (151) [105] 69     | (160) [112] 70 p   | (167)   119   77 w | (176)   126   7E - |

| GKAPHIC SYMBULS | (141)  97] 61 a   |        | (150)   104 ] 68 h | (157) [111] 6F o   | (166) [118] 76 v   | (175)   125   7D } |

| GRA             | (140) [96] 60     | •••••• | (147) [103] 67 9   | (156) [110] 6E n   | (165)   117  75 u  | (174)   124 J 7C i |

|                 | (137) [95] 5F     |        | (146) [102] 661    | (155)   109   6D m | (164)   116 ] 74 ( | (173) [123] 7B {   |

| Нех             | (136) [94 ] 5E    |        | (145) [101] 65 e   | (154) [108] 6C     | (163)   115   73 s | (172) [122] 7A z   |

CEAPHIC SYMBOLS

Octal ( ) Decimal [ ]

### CONFIGURATION

| INTRODUCTION                      | 2-19 |

|-----------------------------------|------|

| MOTHERBOARD CONFIGURATION         | 2-19 |

| S-101                             | 2-19 |

| Jumpers J101 Through J111         | 2-20 |

| VIDEO BOARD CONFIGURATION         | 2-22 |

| DISK CONTROLLER (H/Z-207)         | 2-24 |

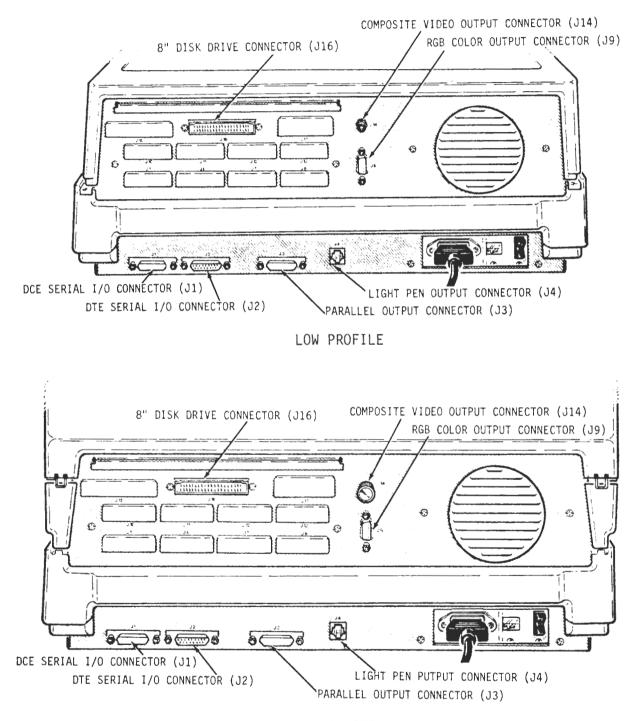

| OUTPUT CONNECTORS                 | 2-26 |

| Serial I/O Connector (J1)         | 2-27 |

| Serial I/O Connector (J2)         | 2-27 |

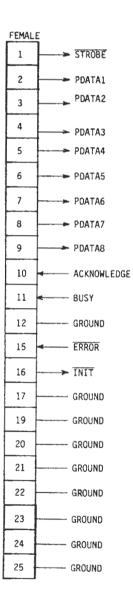

| Parallel Output Connector (J3)    | 2-28 |

| Light Pen Output Connector (J4)   | 2-29 |

| Color Output Connector (J9)       | 2-29 |

| Composite Video Output Connectors |      |

| (J14, Low Profile Only)           | 2-29 |

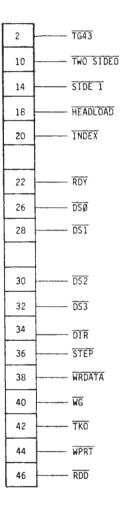

| 8" Disk Drive Connector (J16)     | 2-30 |

| PRINTER CONFIGURATIONS            | 2-31 |

| MX-80 Printer                     | 2-31 |

| H/Z-25 Printer                    | 2-32 |

| H/WH-14 Printer                   | 2-32 |

| Diablo 630 Printer                | 2-33 |

| Diablo 1640 Printer               | 2-33 |

| NEC VIDEO MONITOR CONFIGURATION   | 2-34 |

| INTERNAL DISK DRIVE CONFIGURATION | 2-35 |

\_. \_. . . . \_\_\_\_

\_\_\_\_

. . . -.

- -----

### INTRODUCTION

The H/Z-100 is a versatile computer. Due to this versatility, many different configurations are possible. This section provides the basic information on how the computer may be configured.

### MOTHERBOARD CONFIGURATION

### S-101

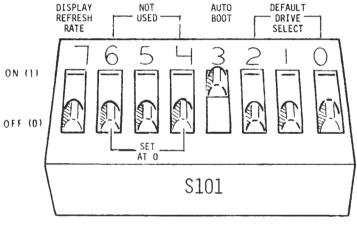

The 8-section slide switch (S101) on the motherboard determines the condition of the computer upon power-up or reset. The sections of S101 are defined as follows:

| Section | Definition                                                  |  |  |

|---------|-------------------------------------------------------------|--|--|

| 0-1-2   | The positions of these bits<br>determine the default drive. |  |  |

|         | 000 = 5-1/4".<br>100 = 8".<br>010 = Winchester.             |  |  |

| 3       | This bit determines auto-boot.                              |  |  |

|         | 0 = manual booting.<br>1 = Auto-boot.                       |  |  |

| 4       | Not used. Leave at O.                                       |  |  |

| 5       | Not used. Leave at O.                                       |  |  |

| 6       | Not used. Leave at O.                                       |  |  |

| 7       | This bit determines refresh rate of the display RAM.        |  |  |

|         | 0 = 60 Hz.<br>1 = 50 Hz.                                    |  |  |

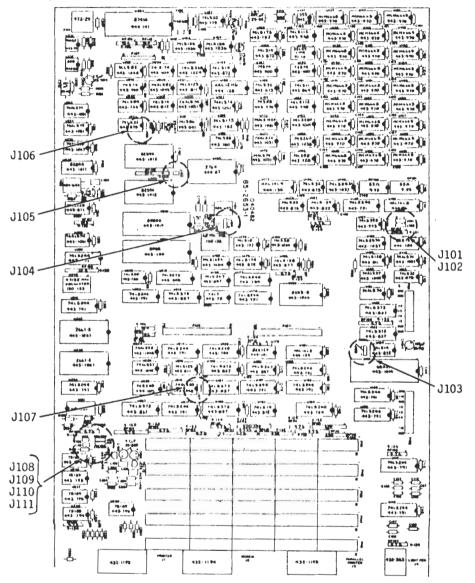

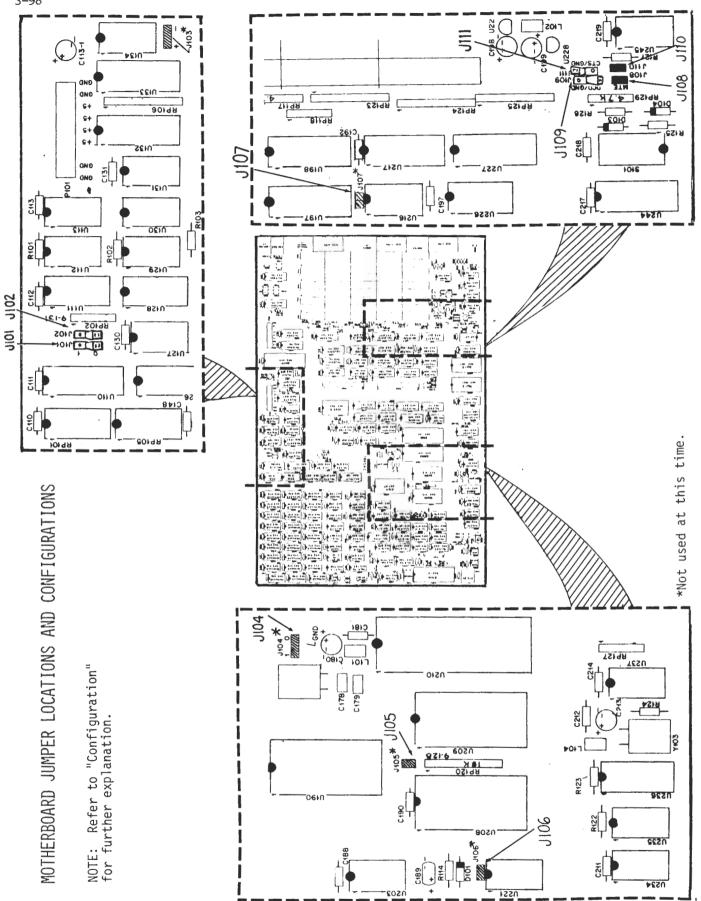

### JUMPERS J101 THROUGH J111

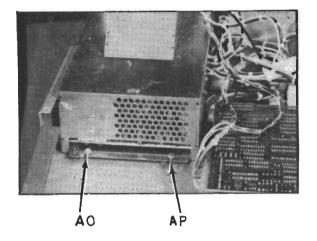

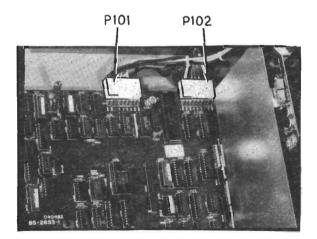

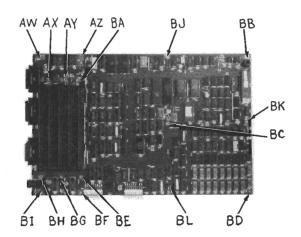

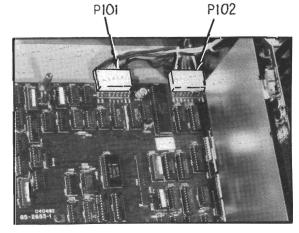

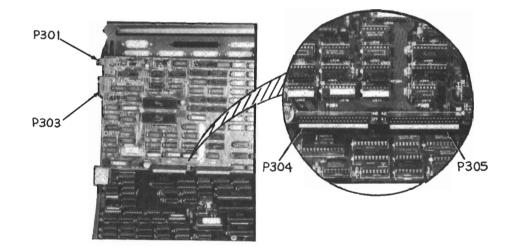

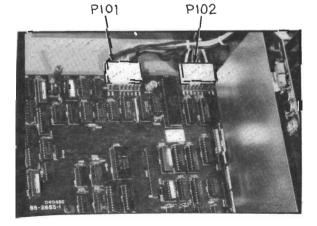

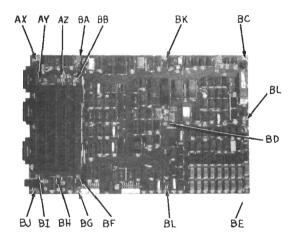

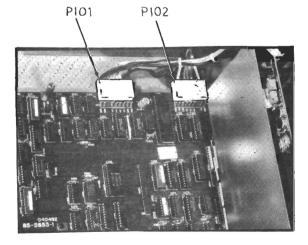

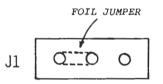

Refer to the pictorial below when reading through the jumper descriptions.

<u>J101 and J102</u> determine the size of ROM that may be installed.

| ROM         | <u>J101</u> | J102 |

|-------------|-------------|------|

| 2764 (8K)   | 0           | 0    |

| 27128 (16K) | 1           | 0    |

| 27256 (32K) | 0           | 1    |

The 27128 and 27256 ROMs are not used in the H/Z-100 at this time, but may be supported in the future.

J103 determines the polarity of the light pen. The markings on the PC board are self-explanatory. The light pen is not supported at this time.

$\underline{J104}$  is jumpered by a foil run on the motherboard to the 1 position. This connection jumpers the NMI line to ground.

$\underline{J105}$  when jumpered, grounds the test pin of the 8088 microprocessor. J105 is not used at this time.

$\underline{J106}$  is not used at this time. This position is normally unjumpered.

J107 is jumpered by a foil run on the motherboard. This position will be shorted regardless of a jumper.

J108 determines whether or not pin 18 (TxEMP) of U242 is connected to the serial interrupt line (EPCIBINT). When using Heath peripherals, this jumper location is normally unjumpered.

<u>J109</u> and <u>J111</u> determine the handshaking protocol of IC U243. This port will support many different printers through the positioning of these jumpers. J109 determines whether pin 16 (DCD) of U243 is connected to the RTS line or ground. J111 determines whether pin 17 (CTS) of U243 is connected to the RTS line or ground. Using Heath peripherals, J109 connects DCD to RTS and J111 connects CTS to ground. If the H/Z-100 you are servicing is not set up in the Heath configuration, the jumpers may be connected to support another manufacturer's peripheral. Consult the peripheral manual for proper jumpering.

J110 determines whether or not pin 18 (TxEMP) of U243 is connected to the serial interrupt line (EPCIAINT). The position of this jumper is determined by the peripherial used on this port. When using Heath peripherals, this jumper location is normally unjumpered.

-----

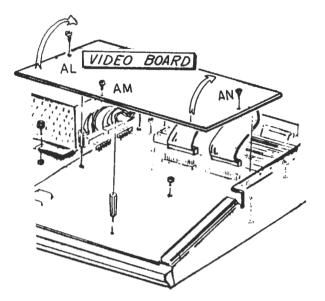

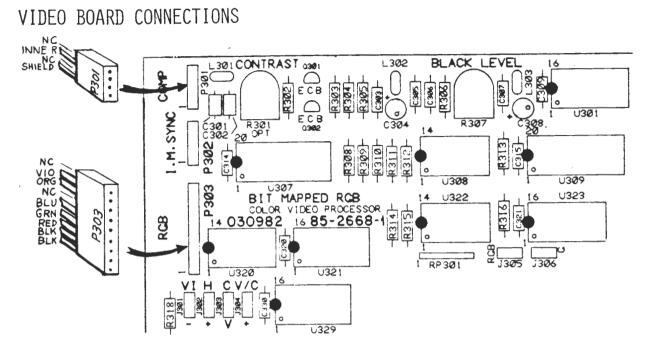

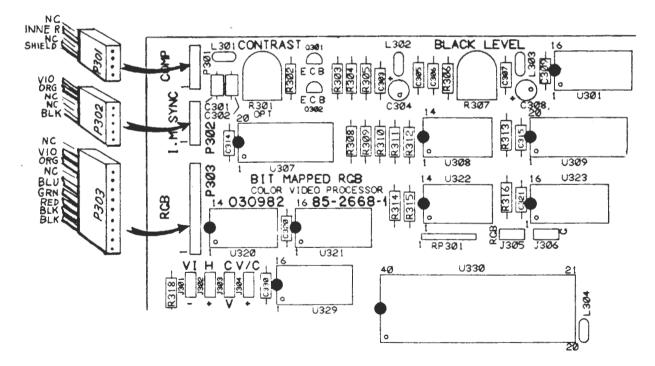

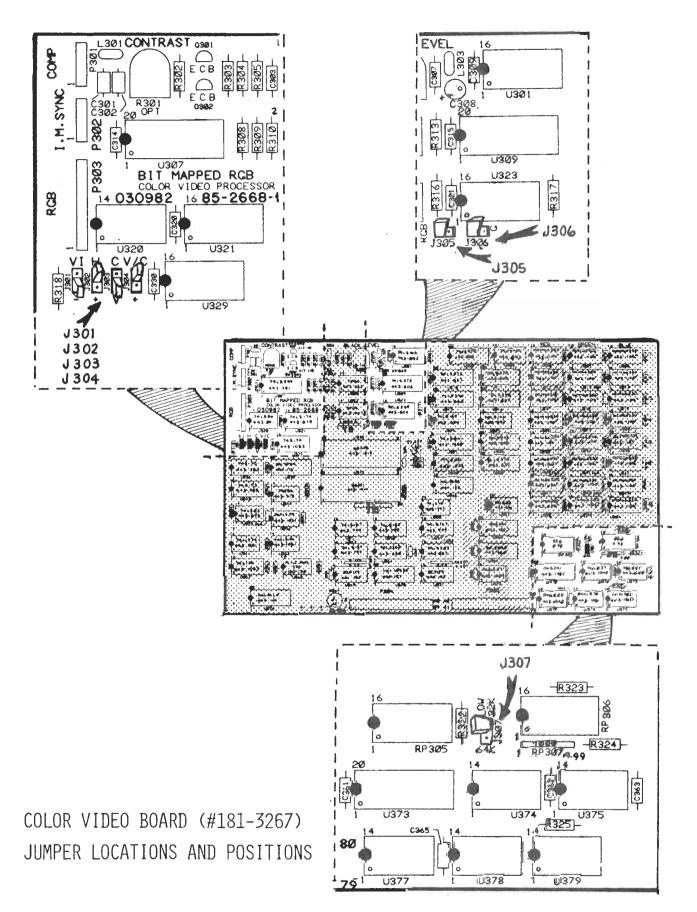

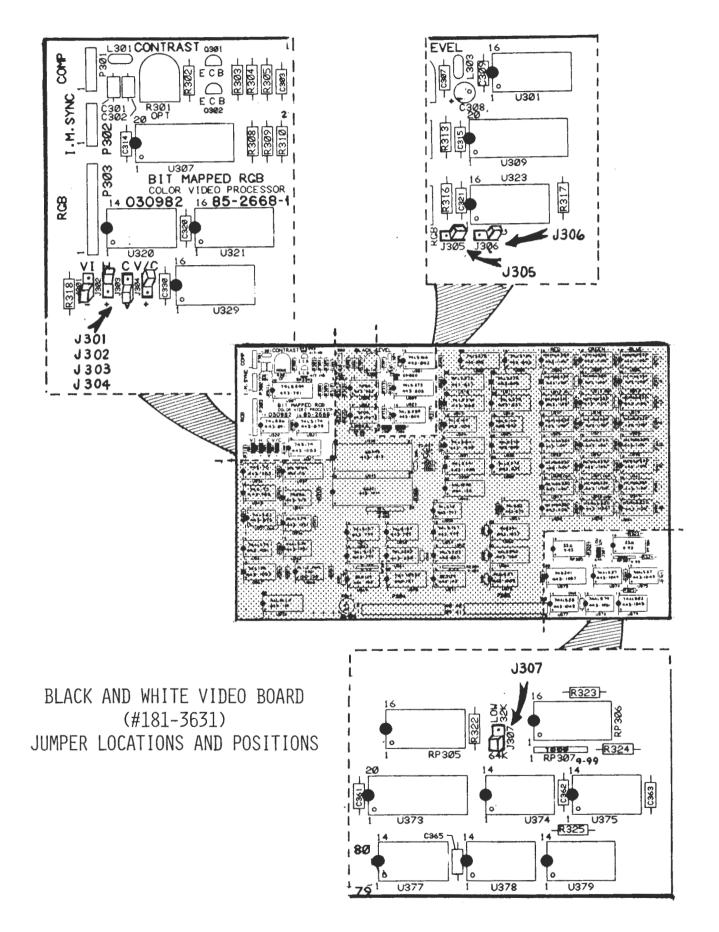

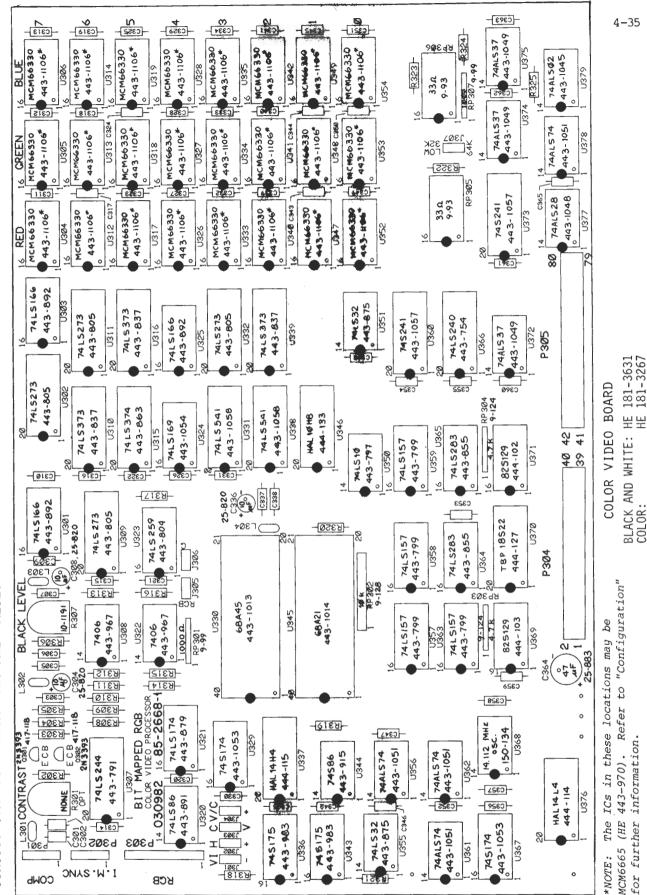

### VIDEO BOARD CONFIGURATION

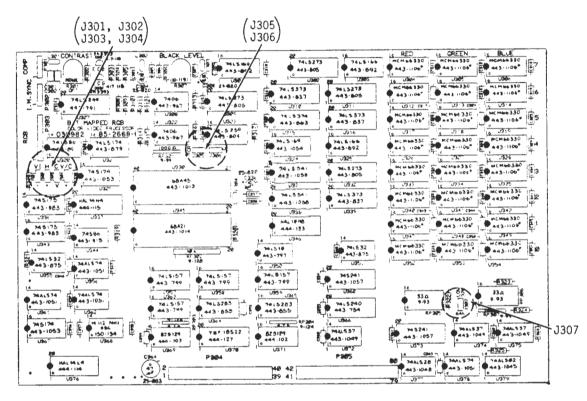

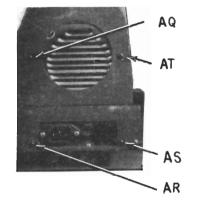

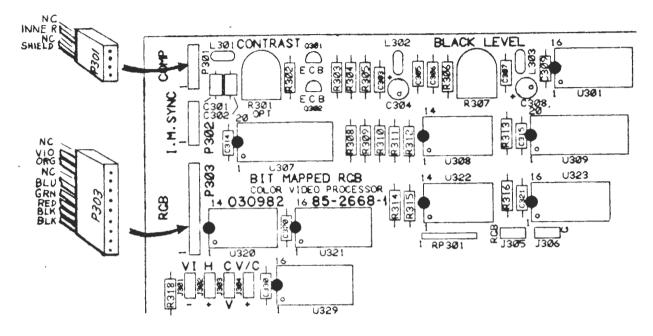

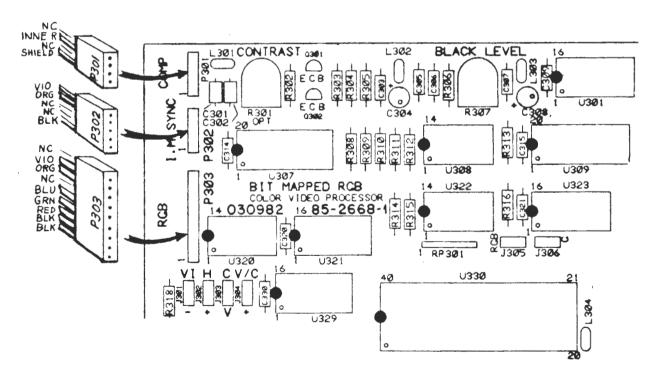

Refer to the pictorial below when reading through the jumper descriptions.

<u>J301</u> determines the polarity of the vertical sync as connected to the internal monitor. The markings on the PC board are self-explanatory. In the Heath mode, this jumper is set for negative vertical sync.

$\underline{J302}$  determines the polarity of the horizontal sync. The markings on the PC board are self-explanatory. In the Heath mode, this jumper is set for negative horizontal sync.

<u>J303</u> determines whether the signal at pin 9 of the RGB cable assembly is composite sync or vertical sync. When the jumper is in the CV position, the signal at pin 9 of the RGB cable assembly is composite sync. When the jumper is in the V position, the signal at pin 9 of the RGB cable assembly is vertical sync.

$\underline{J304}$  determines the polarity of the vertical sync as connected to the RGB cable assembly. The markings on the PC board are self-explanatory. In the Heath mode, this jumper is set for negative vertical sync.

<u>J305</u> and <u>J306</u> determine the type of video signal that is to be available. When the jumpers are in the RGB position, the output video signal will support a color or an 8-level gray scale output. When the jumpers are in the G position, the video output will be a monochrome signal. If the video board contains only one bank of RAM, these jumpers must be set at G.

<u>J307</u> determines how the individual 64K RAM banks will be addressed. When no jumper is installed, the video board will address the high 32K end of the 64K bank. When the jumper is installed in the 32K position, the video board will address the lower 32K end of the 64K bank. When the jumper is installed in the 64K position, the video board will address a 32K section within the 64K bank. NOTE: An advanced programmer may address the whole 64K bank of RAM if he alters the operation of the CRTC. This, however, is not supported at this time. To further explain the jumpering of these two jumpers, the RAM chips that may be installed in the banks must be discussed.

There may be two primary RAM chips installed on the video board; 64K or 32K chips. The 32K RAM chips are further divided in two categories; high end 32K or low end 32K chips. Because 32K RAM chips are actually 64K chips that failed in either the high or low section of the 64K memory area, the 32K and 64K chips are pin for pin compatible. To tell the difference between the two types of 32K chips, you must first identify the manufacturer. There are two approved manufacturers at this time, Motorola and Okie. Use the chart below to identify high-end or low-end chips.

| Manufacturer | Generic Number | Туре                   |

|--------------|----------------|------------------------|

| Okie         | MSM3732L-20AS  | low end (HE 443-1106)  |

| Okie         | MSM3732H-20AS  | high end (HE 443-1107) |

| Motorola     | MCM66330       | low end (HE 443-1106)  |

| Motorola     | MCM66331       | high end (HE 443-1107) |

Once you have the chips identified, you can set the jumper J307. Remember, you cannot mix low end and high end 32K chips on the video board. You may, however, mix manufacturers. If the majority of chips are high end chips, then all chips must be high end and J307 set accordingly. If the majority of the chips are low end chips, then all chips must be low end and J307 set accordingly. If the chips are 64K RAMs, you must set J307 to the 64K position.

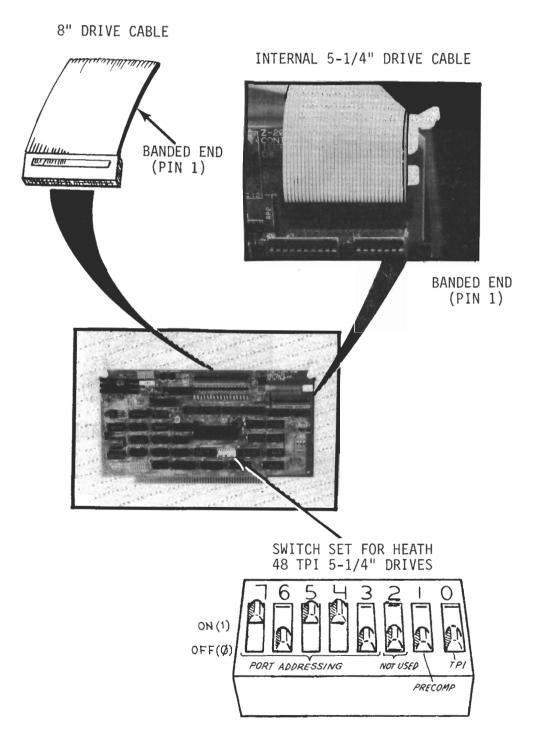

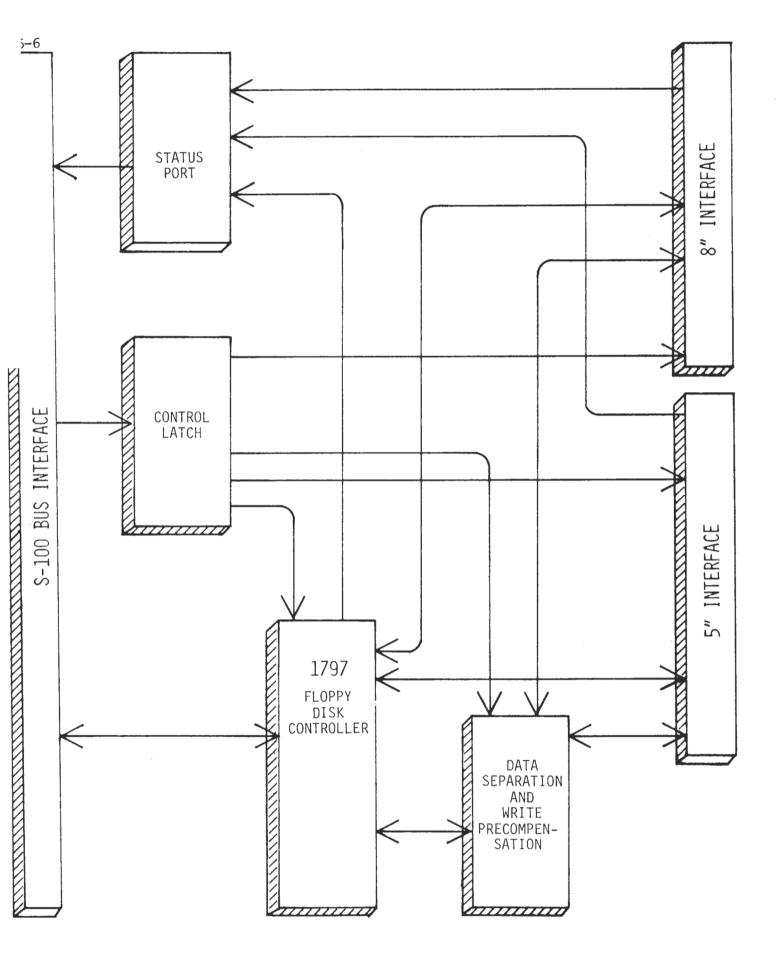

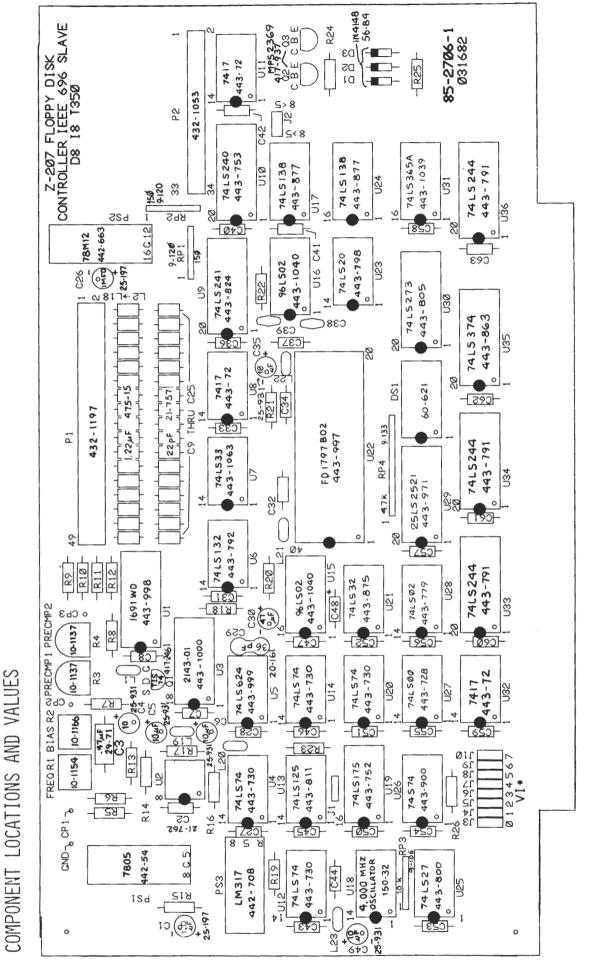

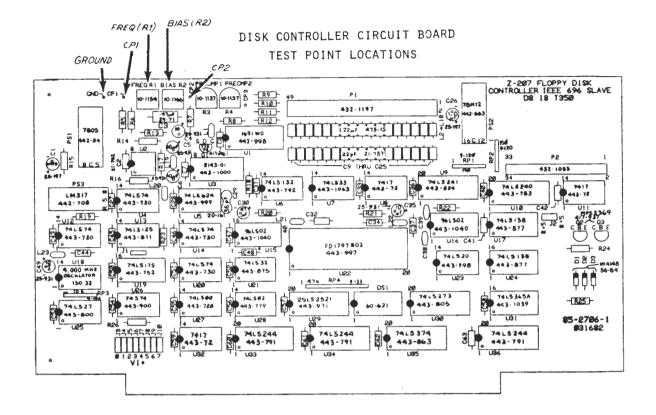

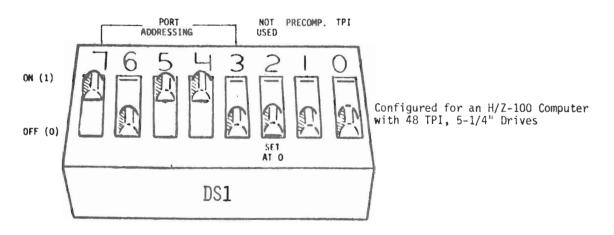

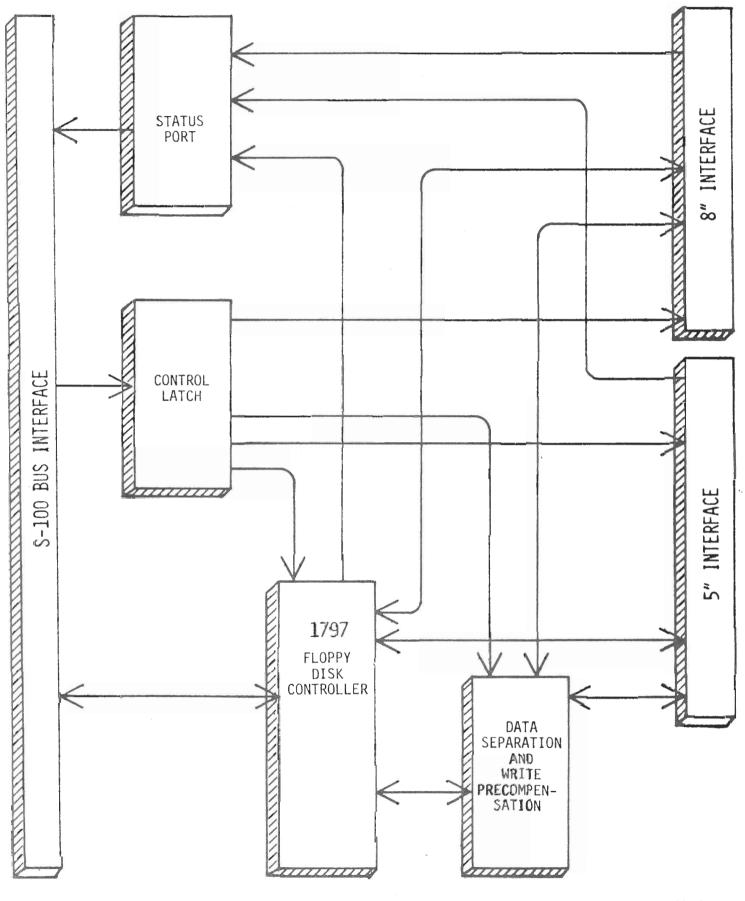

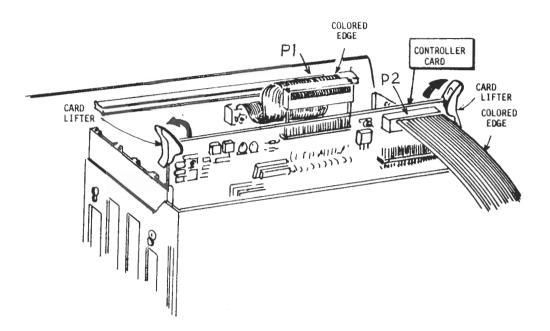

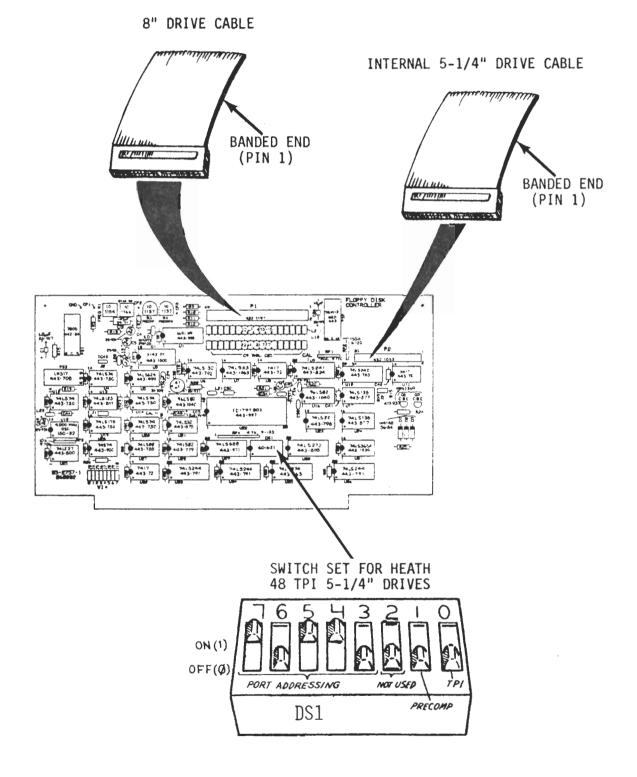

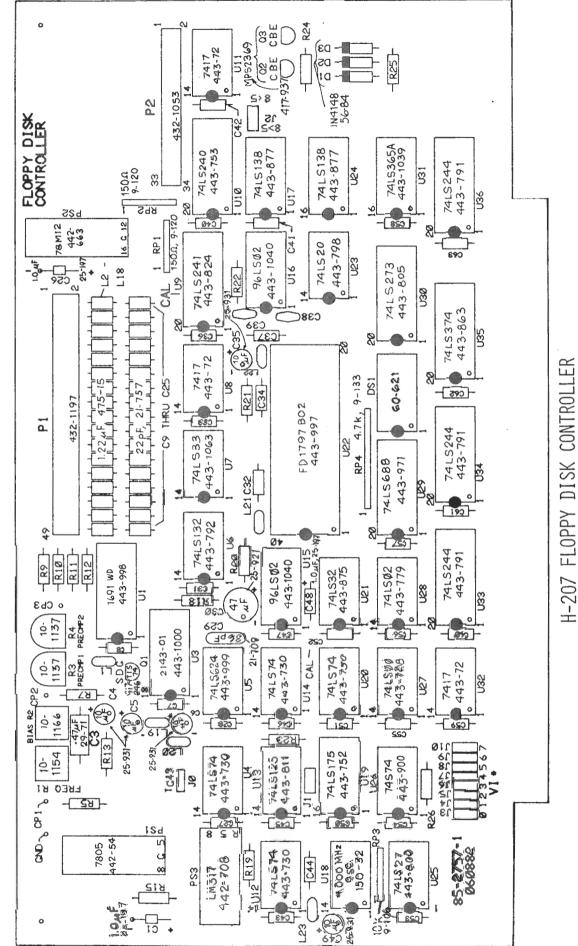

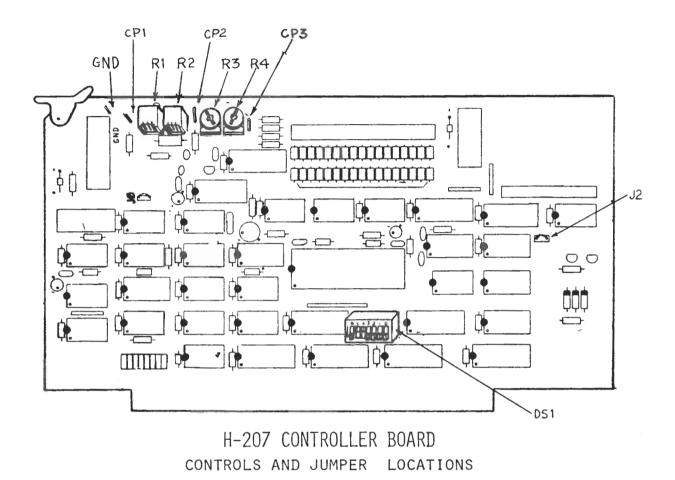

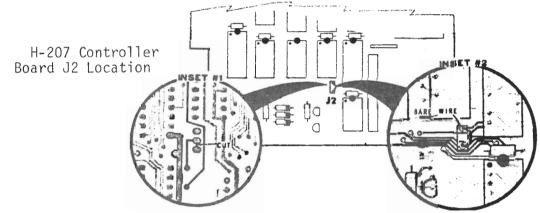

## DISK CONTROLLER (H/Z-207)

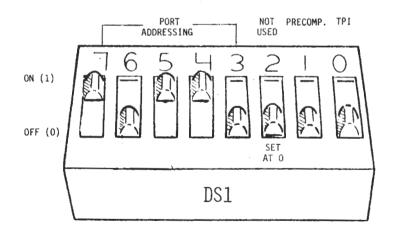

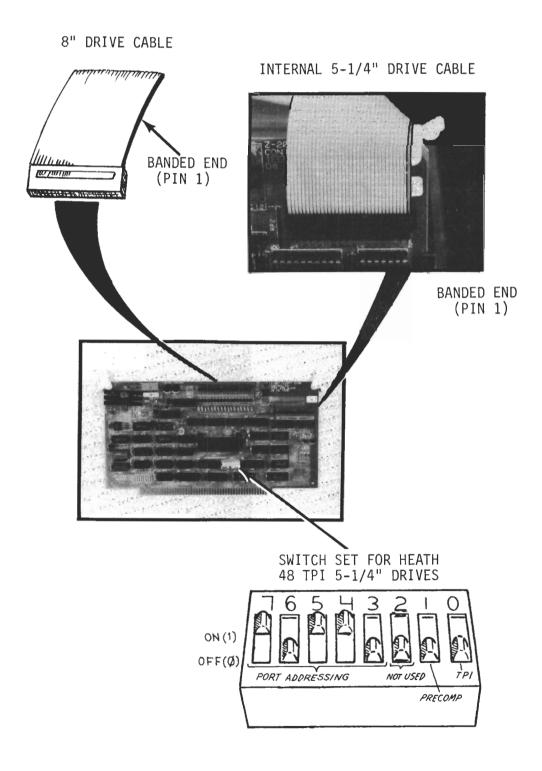

The 8-section slide switch (DS1) on the disk controller board determines the configuration of the board. The sections of DS1 are defined as follows:

| Section   | Definition                                                  |  |

|-----------|-------------------------------------------------------------|--|

| 0         | This bit determines<br>the TPI of the 5-1/4"<br>disk drive. |  |

|           | 0 = 48 TPI.<br>1 = 96 TPI.                                  |  |

| 1         | This bit determines<br>whether precomp is<br>on or off.     |  |

|           | 0 = precomp off.<br>1 = precomp on.                         |  |

| 2         | Not used. Leave at O.                                       |  |

| 3-4-5-6-7 | Port addressing.<br>A port I/O map is shown<br>below:       |  |

| I/O ADDR. (Binary) | READ | WRITE | PORT DESIGNATION      |

|--------------------|------|-------|-----------------------|

| SSSSS000 ·         | х    |       | 1797 Status Register  |

| SSSSS000           |      | Х     | 1797 Command Register |

| SSSSS001           | Х    | Х     | 1797 Track Register   |

| SSSSS010           | Х    | Х     | 1797 Sector Register  |

| SSSSS011           | Х    | Х     | 1797 Data Register    |

| SSSSS 100          |      | Х     | Control Latch         |

| SSSSS101           | х    |       | Status Port           |

|                    |      |       |                       |

\* S = dip switch bit

The dip switch bits are simply defined from the binary equivalent of the switches. An example, port addressing for the H/Z-100, is shown below.

SSSSSXXX \* = 10110XXX = H/Z-100 port B0 - B7. \* X = 1797 register, control latch, or status port.

# OUTPUT CONNECTORS

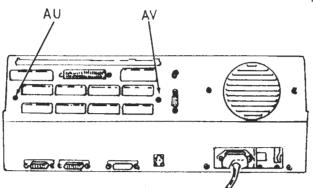

## ALL-IN-ONE

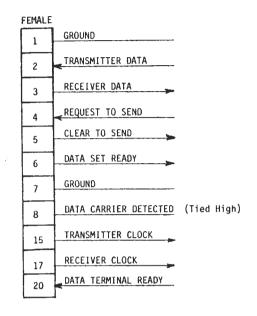

# SERIAL I/O CONNECTOR (J1)

The 25-pin D connector at this location is a RS-232C DCE connector. Its location on the I/O map is port E8 (Hex). The primary use of this connector is for printer operation. For Heath supported printers, refer to "Printer Configuration" (elsewhere in this section) for recommended hardware set-up. Other peripherals and non-Heath printers may require special set up procedures. Use the pinout description and the peripheral's manual for recommended set-up.

# SERIAL I/O CONNECTOR (J2)

The 25-pin D connector at this location is an RS-232C DTE connector. Its location the I/O map is port EC (Hex). The primary use of this connector is for modem operation. Refer to the pictorial below for a description of the pinouts of this connector.

| MALE |                       |

|------|-----------------------|

| 1    | GROUND                |

| 2    | TRANSMITTER DATA      |

| 3    | RECEIVER DATA         |

| 4    | REQUEST TO SEND       |

| 5    | CLEAR TO SEND         |

| 6    | DATA SET READY        |

| 7    | GROUND                |

| 8    | DATA CARRIER DETECTED |

| 15   | TRANSMITTER CLOCK     |

| 17   | RECEIVER CLOCK        |

| 20   | DATA TERMINAL READY   |

|      |                       |

## PARALLEL OUTPUT CONNECTOR (J3)

The 25-pin D connector at this location is a Centronics compatible printer port. Its location on the I/O map is EO (Hex). The primary use of this connector is for parallel printer hookup. Refer to the pictorial below for a description of the pinouts of this connector.

## LIGHT PEN OUTPUT CONNECTOR (J4)

This connector provides the necessary signals to operate a light pen.

### COLOR OUTPUT CONNECTOR (J9)

When the video board has the color option installed, this connector provides the necessary signal to drive an RGB video monitor. Refer to the pictorial below for a description of the pinouts of this connector. Also refer to the video monitor's manual for hookup instructions.

- Pin Signal

- 1 Ground

- 2 Ground

- 3 Red

- 4 Green

- 5 Blue

- 6 Not connected

- 7 Not connected

- 8 Horizontal Sync

- 9 Vertical or Composite Sync

### COMPOSITE VIDEO OUTPUT CONNECTOR (J14, LOW PROFILE ONLY)

This connector is located on the Low Profile model. This connector provides the necessary signals to drive a monochrome video monitor. Refer to the manual of the video monitor for instructions on hookup.

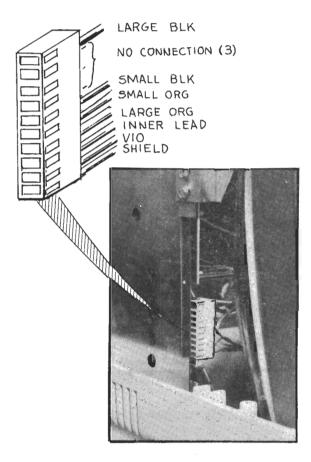

# 8" DISK DRIVE CONNECTOR (J16)

This 50-pin connector provides the necessary signals to drive an 8" Shugart compatible disk drive. Refer to the pictorial below for a description of the pinouts of this connector.

\*All odd numbered pins grounded

# PRINTER CONFIGURATIONS

Refer to the following pictorials for information on how to set the configuration switches within the following Heath supported printers. Handshaking for each of the printers is software supported in Z-DOS using the program "CONFIGUR". For information on the Configur program, refer to the Z-DOS manual or the H/Z-100 User's Manual.

### MX-80 PRINTER

The MX-80 may be connected to the H/Z-100 using either the parallel or serial modes. To use the MX-80 in the parallel mode, set the switches within the MX-80 case as follows:

Remember, the interface cable must be attached to the parallel output connector J3 for the MX-80 to operate in the parallel mode. To use the MX-80 in the serial mode set the switch on the serial board within the MX-80 as follows:

# H/Z-25 PRINTER

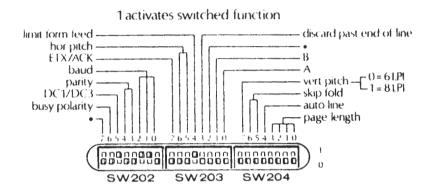

To use the H/Z-25 with the H/Z-100, set switches SW202, SW203, and SW204 as shown below:

# H/WH-14 PRINTER

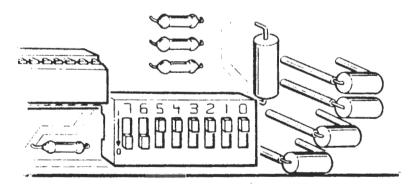

To use an H/WH-14 with the H/Z-100, set switch SW102 as shown below:

### DIABLO 630 PRINTER

To use a Diablo 630 with the H/Z-100, set the internal switches as shown below:

### DIABLO 1640 PRINTER

To use a Diablo 1640 with the H/Z-100, set the internal switches as shown below:

If other manufacturer's printers are being used, refer to its manual to determine proper configuration for that printer.

\_\_\_\_

# NEC VIDEO MONITOR CONFIGURATION

Follow the instructions below to configure the NEC Video Monitor cable for use with the H/Z-100.

- -- Remove the DIN-type connector from the NEC Video Monitor cable (P/N PC-8091A).

- -- Obtain a subminature 9-pin male D connector (Amp P/N 205204-1) and cable clamp assembly (Amp P/N 207908-1).

- -- Remove 3/4" of outer insulation material from the NEC cable.

- -- Remove 1/4" of insulation from each end of the exposed conductors. Pre-tin each wire.

- -- Connect each of the wires from the NEC cable to the 9-pin connector as follows:

| Quantity | NEC Cable    | D Connector Pinout | Signal      |

|----------|--------------|--------------------|-------------|

| 1        | BR/WHT       | 5                  | Blue Video  |

| 1        | BR/BLK       | 4                  | Green Video |

| 1        | BR/Red       | 3                  | Red Video   |

| 3        | Solid Yellow | 2                  | Ground      |

| 2        | Solid Yellow | 1                  | Ground      |

| 1        | Solid Gray   | 1                  | Ground      |

| 1        | YEL/WHT      | 9                  | V Sync      |

| 1        | YEL/BLK      | 8                  | H Sync      |

|          |              | •                  |             |

-----

-- Assemble the cable clamp assembly.

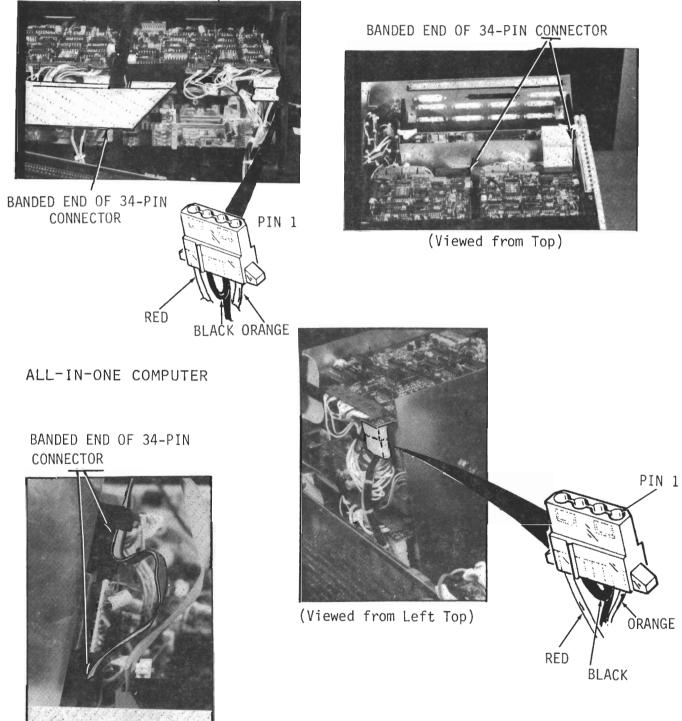

# INTERNAL DISK DRIVE CONFIGURATION

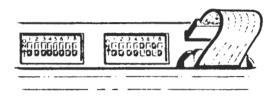

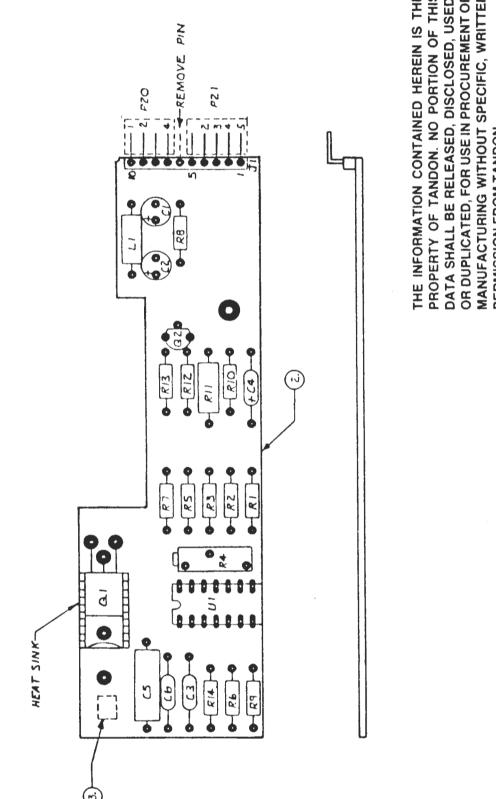

Drive programming for the internal 5-1/4", 48 TPI Tandon disk drives is shown below. On some disk drives the jumper pack shown below may be replaced with a single jumper wire at NDSO or NDS1. This configuration is considered normal since connection across HS is not necessary. If you encounter one of these drives, do not replace the jumper wire with the jumper pack (HE 432-1068). The leads on this jumper pack are too thin and may not make proper contact in the socket. If you do not have a Tandon jumper pack, carefully insert a piece of bare wire (HE 340-8) into the proper location.

The location of the resistor pack is the same as in other Heath or Zenith Data Systems disk drive systems. That is, the resistor pack(s) are removed from all drives except the last hardware unit.

TECHNICIAN NOTES:

. \_ \_\_\_

\_\_\_\_\_

The following characteristics of the H/Z-100 Computer are considered normal. Become familiar with these characteristics. It can save you time by preventing any servicing of the computer for a condition that is considered normal operation.

- -- During the boot process, the cursor will move to a random position in the line "Read Completed". The position of the cursor may change with each boot-up.

- -- The internal 5-1/4" disk drives will not turn off until they time out 18 seconds after the last deselection. Even if a master reset is initiated, the drive motors will stay on until they are timed out.

- -- The computer is sent to the customer in the autoboot mode. If a disk is not installed within 30 seconds after power-up, the display will show a disk error message and the computer will go into the monitor mode.

2-40

,

•

.....

.....

## INTRODUCTION

This block diagram description will show you how the H/Z-100 operates as a system. It starts with the basic blocks and then analyzes what goes on in each block. Once you understand the operation on this level, go on to the circuit descriptions located in the appropriate section of the Blue Book.

The circuit descriptions are written on the level of the experienced microcomputer technician. If you're new to computers, we recommend that you study one of the computer courses available from Heath Company.

Even if you are an experienced computer technician, you may want to review the IC data sheets in the Data Sheets section of this book. The description explains the important features of the more complex ICs affecting circuit operation, but assumes that you know how the ICs work. This is necessary to keep the circuit description from drifting off its intended subject -- the H/Z-100.

Likewise, you should become familiar with the S-100 bus (IEEE-696). The description explains how and why certain lines are developed, but assumes that you're familiar with the bus pin-out and understand the mnemonics used. You can find a description of the S-100 bus in the Appendices section of this manual.

## SYSTEM OVERVIEW

In this block diagram description, we'll cover the major circuits of the H/Z-100 Digital Computer. Though some of these block diagrams appear detailed, several buffers and gates have been left out to keep the illustrations from getting cluttered. As a result, you will see several circuits that appear to connect to the S-100 bus when they may actually be separated from the bus by an octal buffer. The block diagrams do show the buffers where the bus must be multiplexed or demultiplexed.

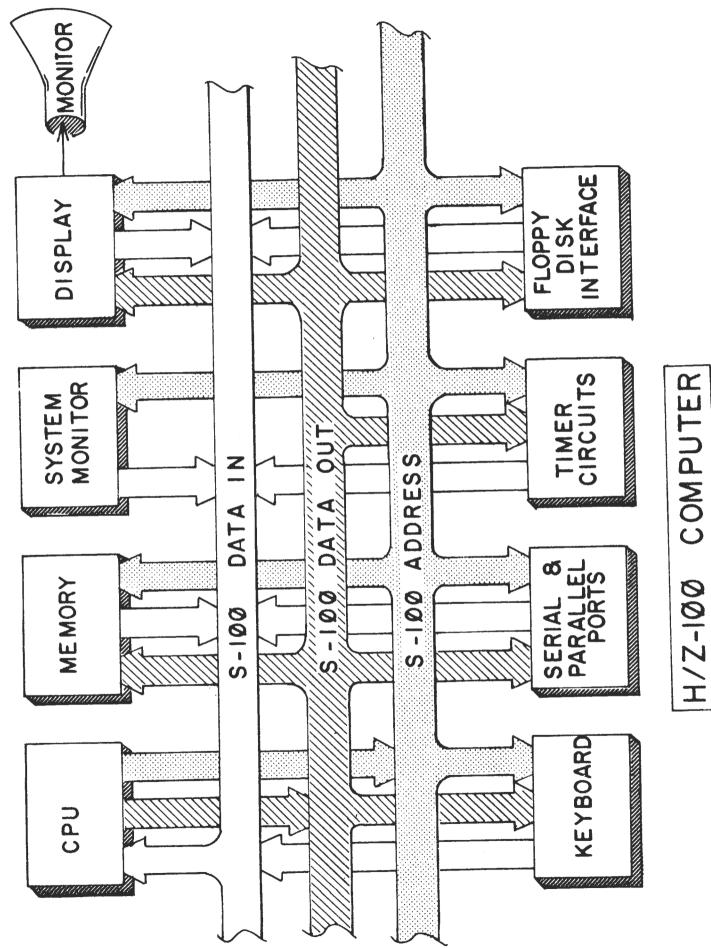

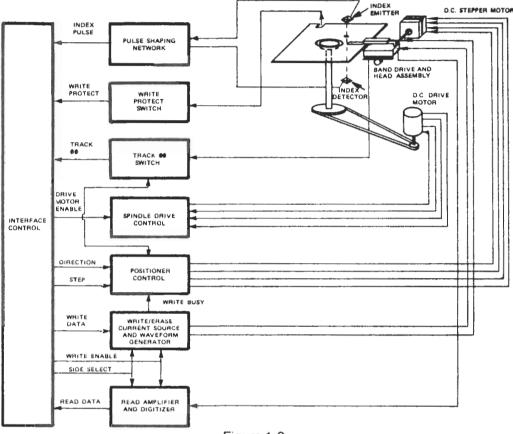

Basically, the H/Z-100 Digital Computer can be broken down to eight major blocks: The CPU, memory, system monitor, display, keyboard, serial & parallel ports, timer circuits, and the floppy disk interface board.

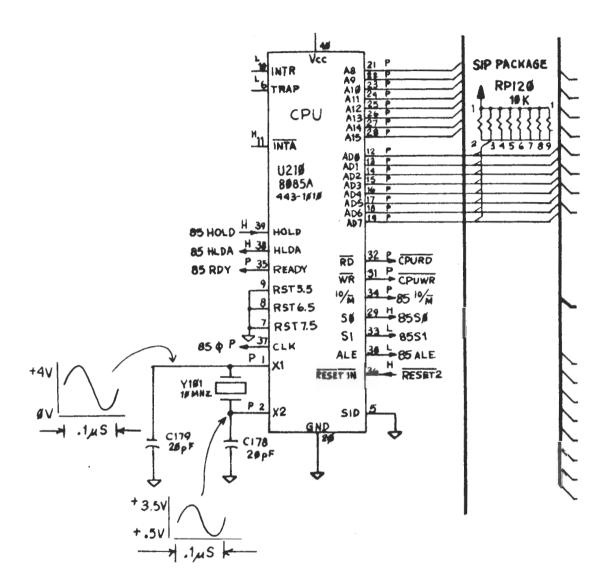

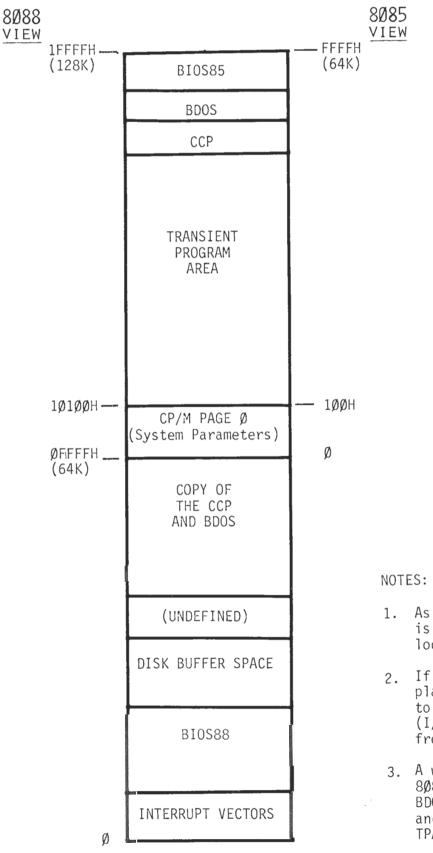

The CPU block consists of two microprocessors; an 8085 8-bit processor and an 8088 16-bit processor. The 8085 permits software compatibility with the existing body of 8080/8085 software while the 8088 provides greater computing power for new applications. Either CPU is software selectable. The 8088 CPU, however, is the active processor after power up or reset.

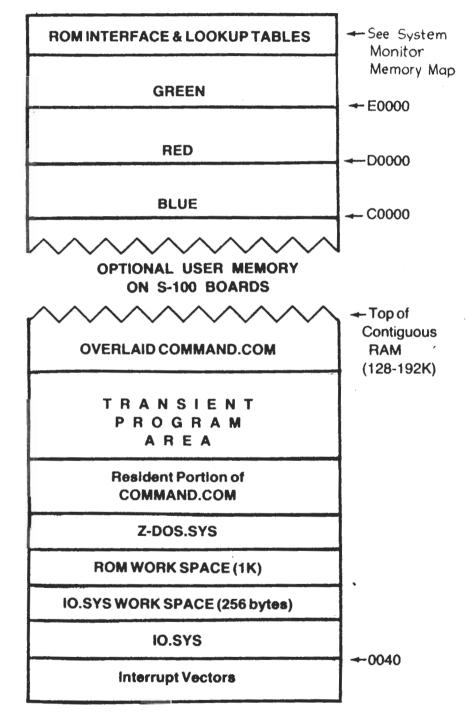

The memory block contains up to three 64-kilobyte banks of RAM for 192K of read/write memory. The memory circuits provide refresh to prevent data loss when the CPU isn't accessing memory. This block also has an arbitration circuit to ensure that refresh doesn't occur when the CPU is accessing RAM, and that the CPU won't access RAM while a refresh operation is taking place. The system monitor takes control of the CPU after power up or reset. Through it, the CPU programs the I/O circuits to allow communicating with the user.

The display circuits provide a video graphics output from the computer. This can be monochrome or color. The display circuits can contain up to 192K of RAM; 64K for each primary color (red, green, blue). After reset, the system monitor programs the display circuits to print alphanumeric characters when the appropriate keyboard key is pressed. However, the display memory can be directly addressed by the CPU, permitting graphics.

The keyboard circuits are built around a dedicated microprocessor that interfaces the matrix keyboard to the CPU. Through software control, the keyboard can output either the normal ASCII character set, or a special event-driven character set for real-time applications. The keyboard circuits also contain oscillators for bell and key-click sounds.

The serial and parallel ports permit the H/Z-100 to communicate with outside devices such as MODEMs, printers, and voice synthesizers.

The timer circuits contain programmable counters that the CPU can use for a real-time clock, a calendar, or for other events-related functions. This circuit has its own oscillator, so the CPU doesn't need to spend any time periodically updating the count.

The floppy disk interface permits connecting up to four 8" and four 5" floppy disk drives to the H/Z-100. This is the only circuit in this block diagram that plugs into the S-100 bus. Though the other circuits communicate through the S-100 bus, they are all located on either the motherboard or the video board. See the Disk Controller and Drives section of this Blue Book for more information on the interface board.

The block diagram also shows three of the major S-100 buses; data in, data out, and address. Both data buses are 8 bits wide; if the CPU fetches a 16-bit instruction, it transfers it a byte at a time. The address bus is 24 bits wide, allowing the CPU to directly address up to 16 megabytes of memory.

Note that the data directions are referenced to the CPU. Data from the top bus goes IN to the CPU. Data from the CPU goes OUT to memory or a port through the middle bus.

## DETAILED LOOK

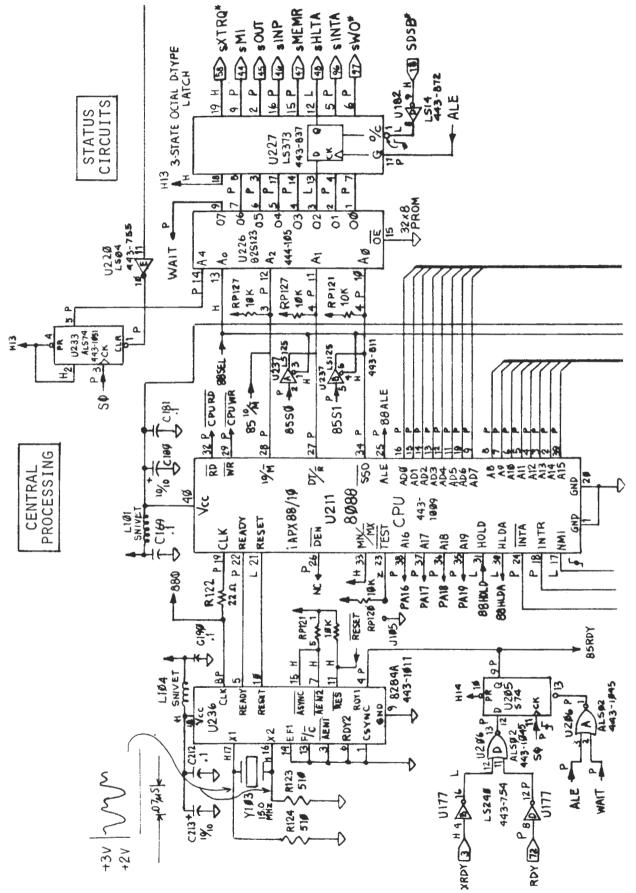

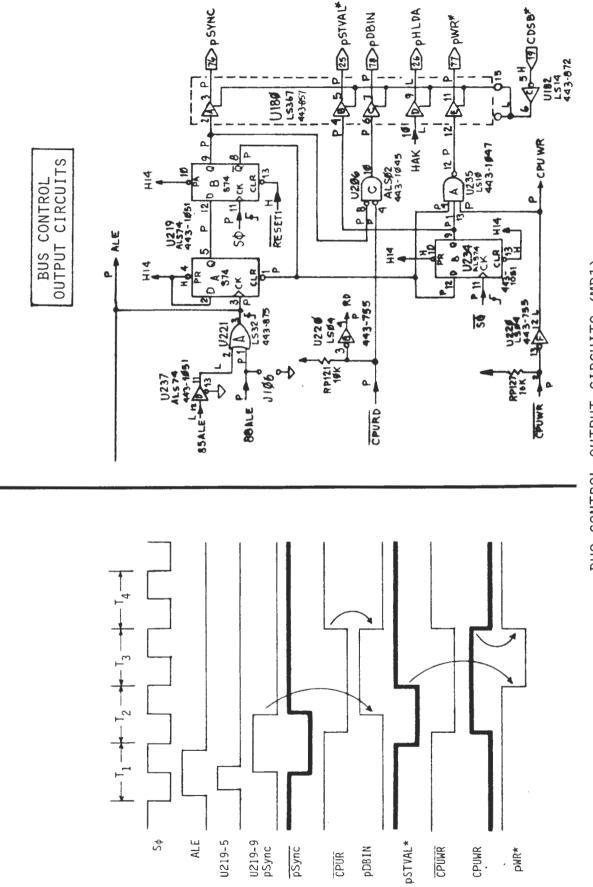

CPU AND S-100 BUS

### READING AND WRITING DATA

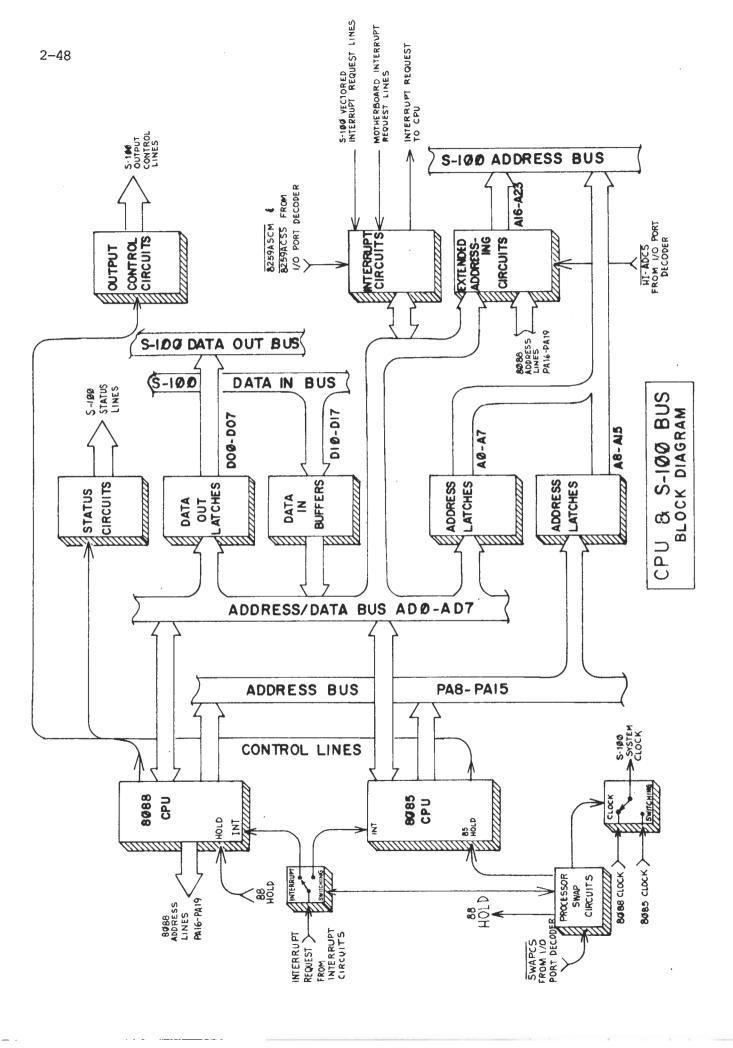

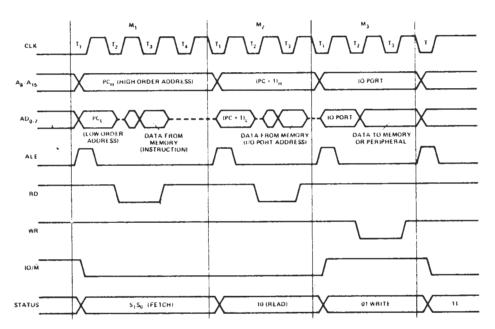

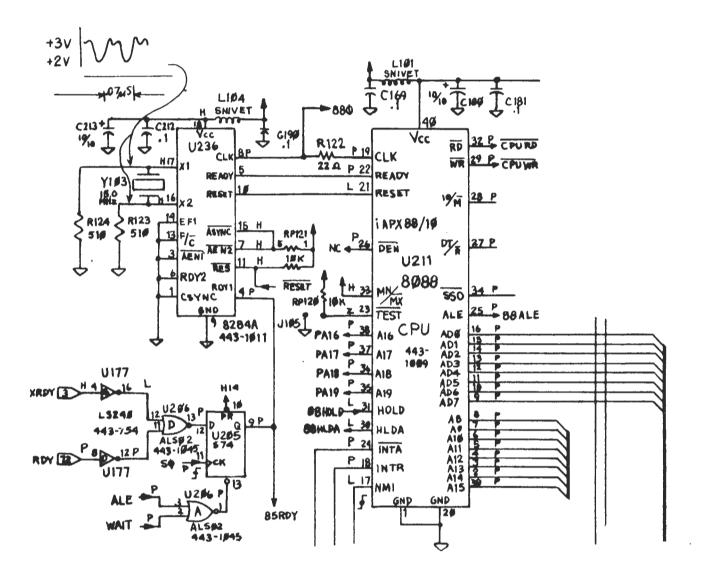

The 8085 CPU is an 8-bit internal, 8-bit external processor. It is software compatible with the 8080 CPU and can directly address up to 64 kilobytes of memory. The 8088 CPU is a 16-bit internal, 8-bit external processor. It is software compatible with the 8086 CPU and can directly address up to 1 megabyte of memory. This is due to the extended-address lines, PA16-PA19.

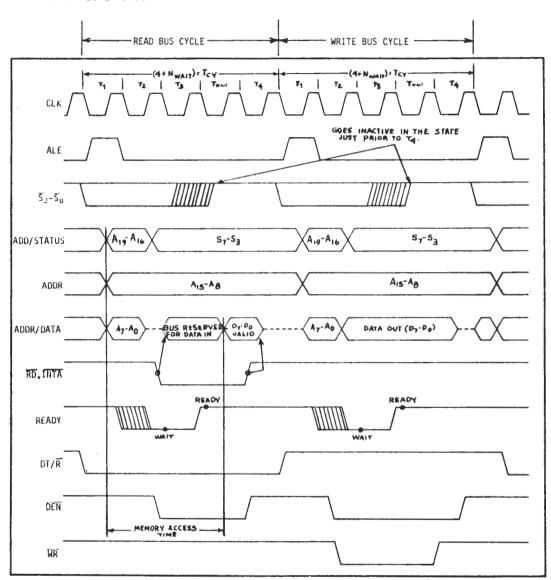

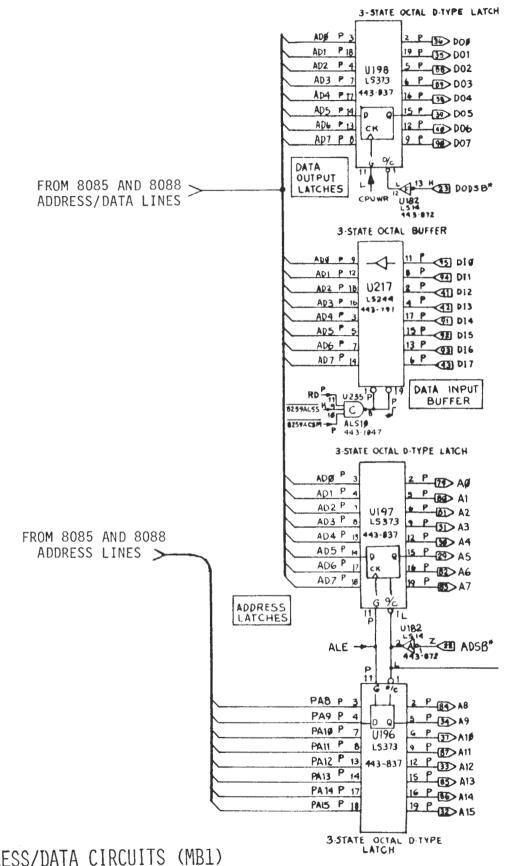

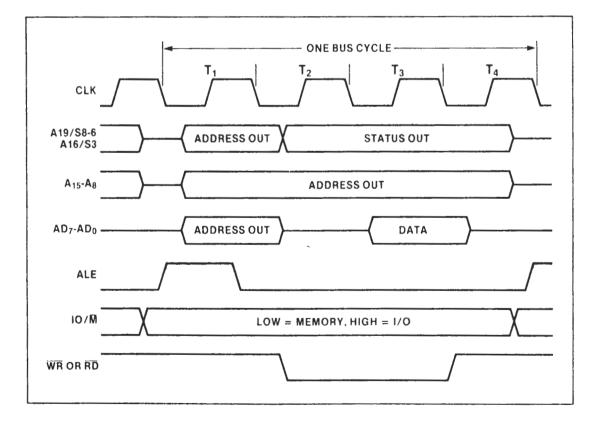

Except for lines PA16-PA19, the 8088 address, data, and control lines function in the same manner as those of the 8085. The lower 8 bits of the address bus is multiplexed with the data bus. Whenever either CPU accesses memory, it first places the address on lines ADO-AD7 and PA8-PA15. This information is latched into the address latches shown in the lower center of the block diagram. The outputs of these latches connect to lines AO-A15 of the S-100 bus.

Next, if writing data, the CPU places the data onto lines ADO-AD7 and latches it into the data-out latch. The output of the latches connects to lines DOO-DO7 of the S-100 data output bus. When the data and address lines are stable, the CPU control lines activate certain lines in the status circuits and the output control circuits to write the data into the addressed memory location.

The operation is almost the same for reading from memory. In this case, however, once the address lines are stable, the status and output control lines will cause the addressed memory location to place the data byte onto the S-100 data-in bus. It is then coupled through the data-in buffers and loaded into the CPU.

### EXTENDED ADDRESSING

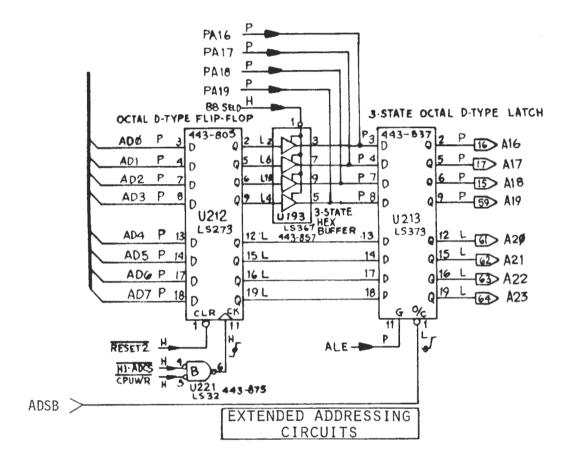

The extended addressing circuits provide up to 16-megabyte addressing capability, in accordance with the IEEE-696 standards. It does this by latching data onto address lines A16-A23.

When the 8088 is active, the extended address lines couple the 8088 extended address lines, PA16-PA19, to A16-A19 of the S-100 bus. Thus the 8088 is able to access its normal 1-megabyte address space.

If the 8088 needs to address a location above 1 megabyte, it places the extended address values onto lines ADO-AD7 and asserts HI-ADCS from the I/O port decoder. The extended address circuits disconnect the PA16-PA19 lines and latch the value on ADO-AD7 onto A16-A23 of the S-100 bus.

When the 8085 is active, the extended addressing circuits are normally disabled; lines A16-A23 are zero so the 8085 is operating within the first 64K bank of memory.

If the 8085 needs to address a location above 64 kilobytes, it places the extended address values onto lines ADO-AD7. It then asserts HI-ADCS to latch this value onto A16-A23 of the S-100 bus.

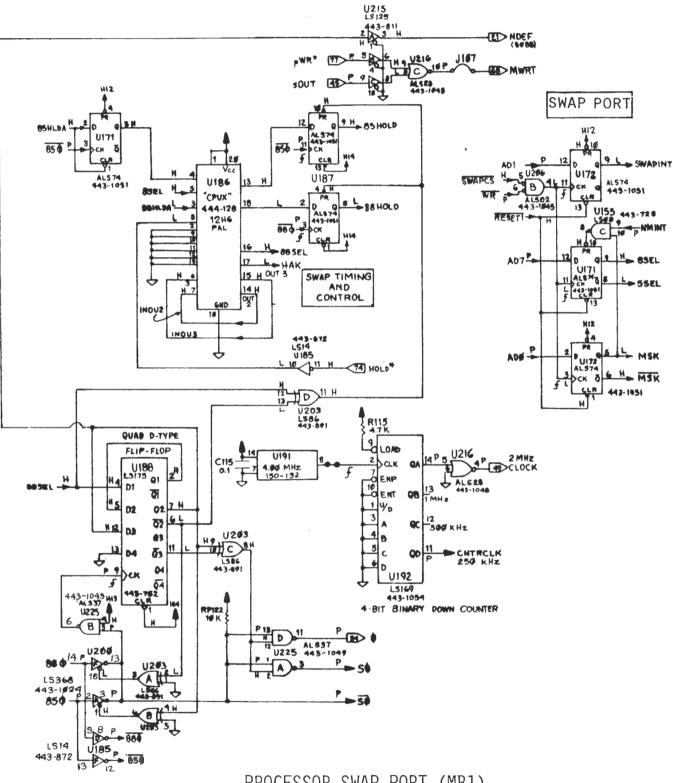

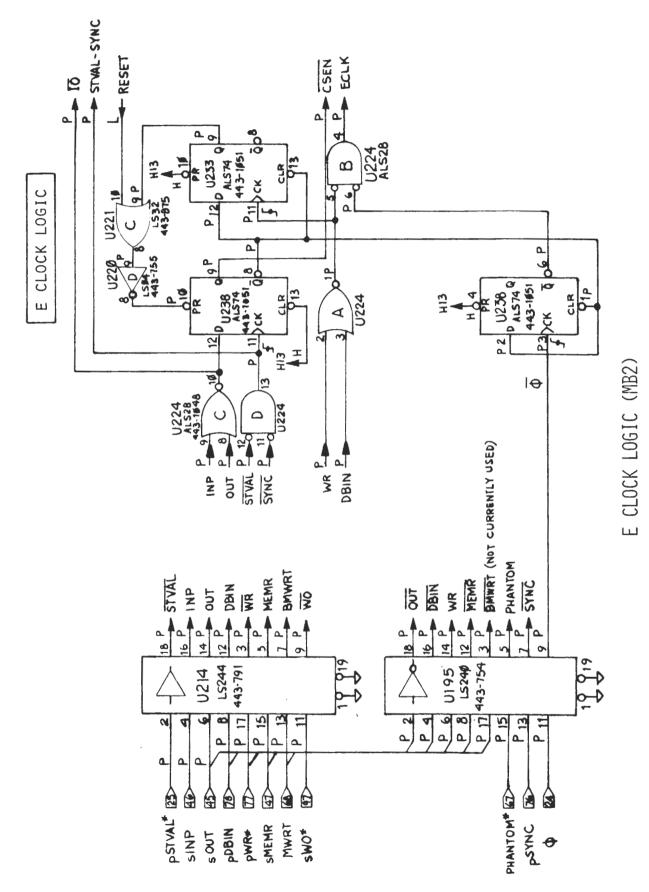

#### PROCESSOR SWAP CIRCUITS

The processor swap circuits handle all the switching necessary to disable one CPU and enable the other. It is activated by asserting SWAPCS from the I/O port decoder and sending a control word from the active CPU to the swap circuits.

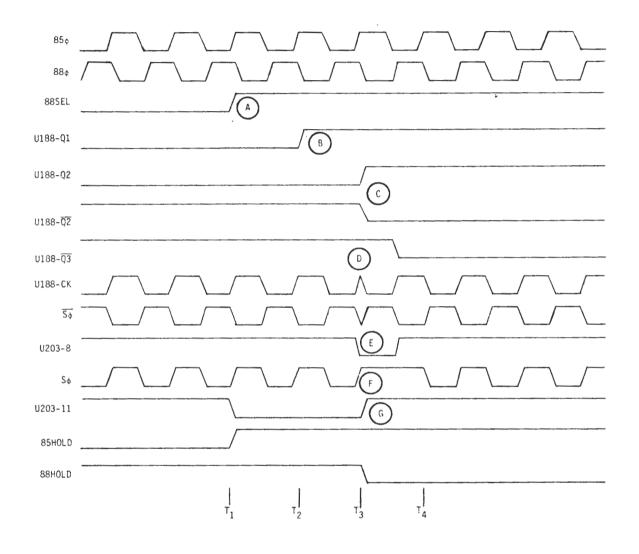

The swap circuits switch CPUs by asserting the proper HOLD line. For example, if switching from the 8085 to the 8088, the 85HOLD line will go high to disable the 8085, and the 88HOLD line will go low to enable the 8088.

The swap circuits also determine whether the 8088 clock or the 8085 clock is coupled to the S-100 system clock line. Although these 5-MHz clocks are crystal controlled, they aren't in phase. To ensure that a spike doesn't occur, the clock switching circuits hold the system clock line at its previously-valid logic state until the incoming signal matches it.

For example, if the system clock is logic one when the H/Z-100 swaps from the 8085 to the 8088, it will remain high until the 8088 clock is logic one. Once this occurs, the 8088 clock is allowed to pass to the S-100 system clock line.

The processor swap circuits also control the interrupt switching circuits. These circuits ensure that any interrupt request is routed to the currently-selected processor. These circuits also have a masking feature that forces the 8088 to handle all interrupts.

If, for example, the 8085 is active and the mask mode is selected, the 8085 will continue to operate until an interrupt request occurs. The interrupt switching circuits cause the processor swap circuits to disable the 8085 and enable the 8088. The interrupt switching circuits then route the interrupt request to the 8088. After the interrupt is processed, it is up to the interrupt-handler program to return control to the 8085.

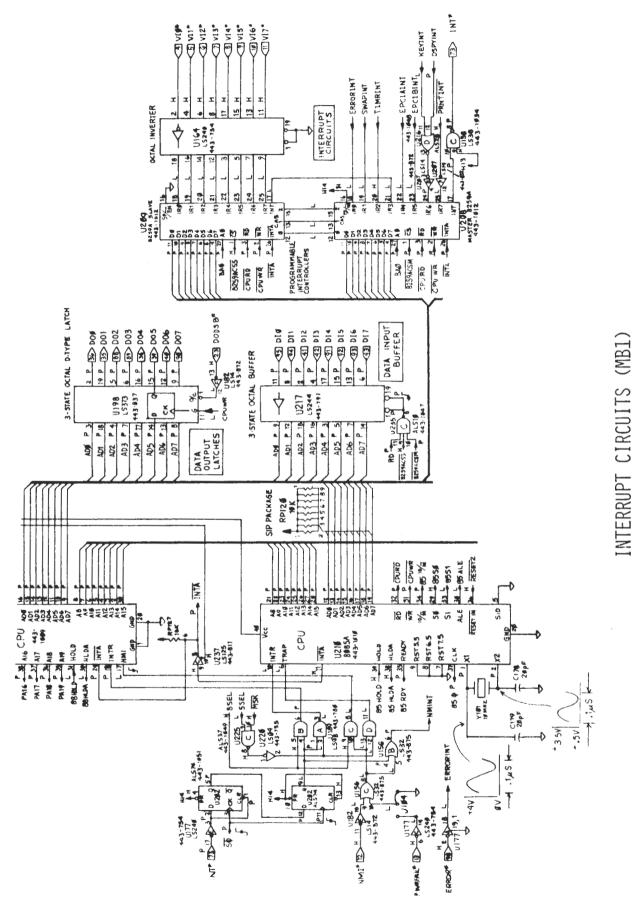

### INTERRUPT CIRCUITS

The interrupt circuits monitor various circuits on the motherboard and notify the CPU if any of the circuits have data that requires immediate attention. These circuits include the various I/O ports, the timer, and memory parity. Also, the interrupt circuits monitor the vectored interrupt lines which are used by S-100 boards, such as the Z-207 floppy disk interface board.

The interrupt circuits are programmable through the address/ data bus and the chip-select lines, 8259ACSM and 8259ACSS. Programming options include: masking out unwanted interrupts, selecting the interrupt priority, and setting up the pointer to the interrupt-handling routine.

....

MEMORY CIRCUITS

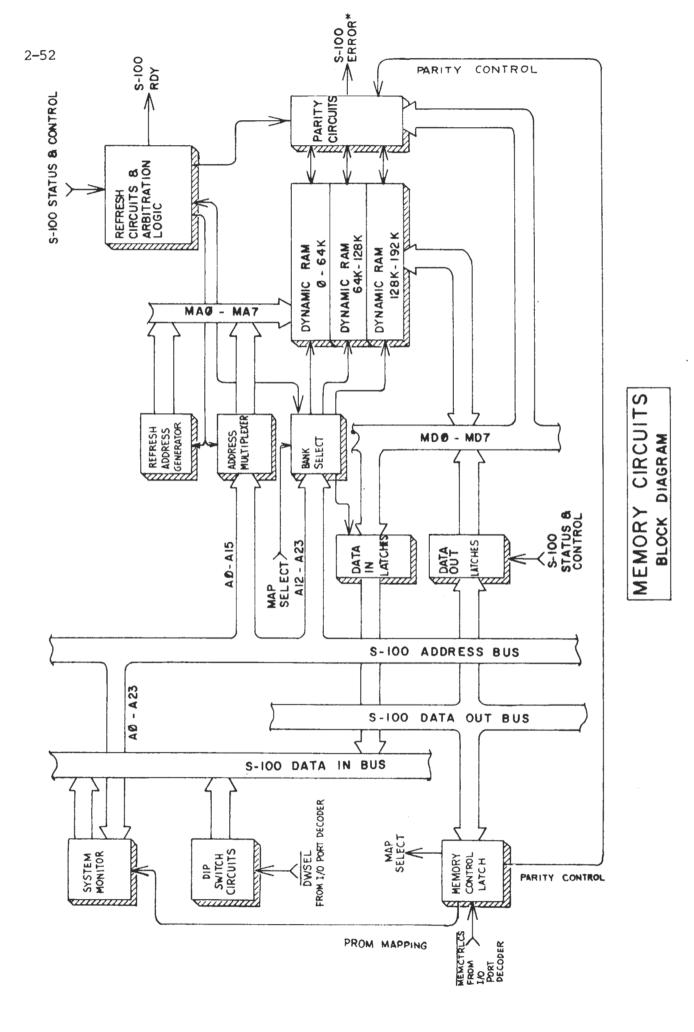

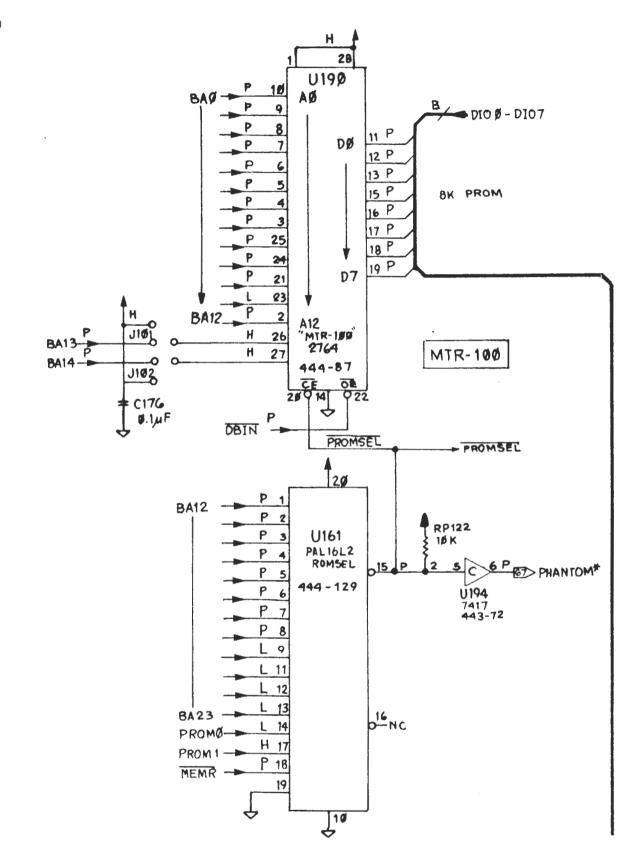

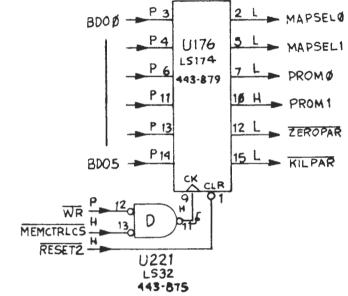

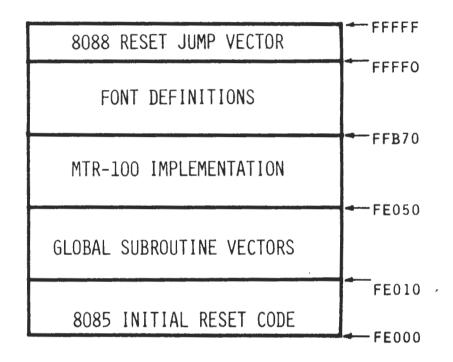

#### SYSTEM MONITOR

The system monitor is an 8K ROM that can be relocated in memory through software control. This is done by the PROM mapping signal from the memory control latch. The memory control latch is programmed by sending it a control word from the CPU and asserting the MEMCTRLCS line from the I/O port decoder.

There are four relocating options available to the system monitor:

<u>Option 0</u> makes the ROM appear to be in all memory locations whenever a memory read is performed. Memory writes still take place normally. This is the option selected immediately after power-up/reset. The 8085 is in control of the H/Z-100, switches to the 8088, and then selects Option 2 for the system monitor.

<u>Option 1</u> puts the ROM at the top 8K of every 64K page of memory. This is useful for the 8085, which has only a 64K natural address space.

<u>Option 2</u> gates the ROM to appear in the top 8K of the 8088's natural 1 megabyte address space. This is the normal operating option when the 8088 has control of the H/Z-100.

$\underline{Option\ 3}$  disables the ROM. The ROM is not accessible when this mode is selected.

When the ROM is selected, all other memory (except video RAM) is disabled. This allows other memory to share the ROM's address space using the S-100 PHANTOM line.

After reset, the monitor tests the status of the dip-switch circuits to set up the H/Z-100 default operating modes. See the Configuration section of this Manual for the various configurations.

#### DYNAMIC RAM

Read/write memory consists of three 64K banks of dynamic RAM. This permits a total of 192K of onboard memory.

The proper memory location is selected by the combination of the address multiplexer and the bank select circuits. The S-100 address bus couples lines AO-A15 to the address multiplexer and lines A12-A23 to the bank select.

The bank select tests to see if the address is within the 192K address range. If so, it selects one of the three 64K banks. It does this by first asserting the appropriate row address strobe (RAS), followed by asserting the column address strobe (CAS).

When RAS asserts, the address multiplexer places lines AO-A7 onto memory address lines MAO-MA7, which are then latched into the row address registers in memory. When CAS asserts, the address multiplexer places lines A8-A15 onto MAO-MA7. This, plus the row address, points to the correct location in memory.

If the CPU is reading data from memory, the memory circuits will place the addressed byte on the memory data bus, MDO-MD7. Next, the bank select circuits enable the data-in latch to couple the data to the S-100 data-in bus.

If the CPU is writing data to memory, the appropriate S-100 status and control lines enable the data out latches to couple the data to MDO-MD7. From there, the data is written into the correct memory location.

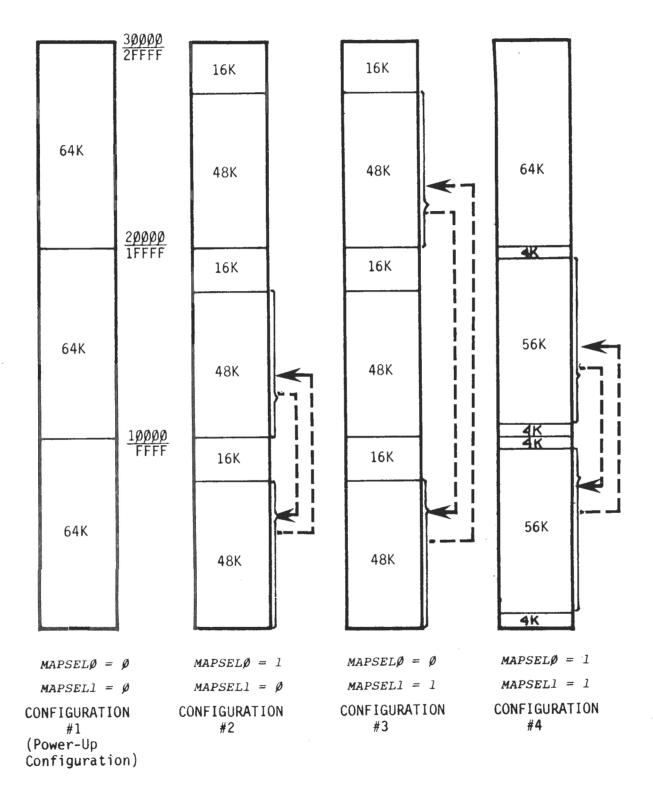

Like the system monitor, portions of the dynamic memory can be relocated to different addresses. There are four options available, these include:

<u>Option 0</u> is the normal configuration. This mode provides contiguous addressing to all of the memory.

<u>Option 1</u> swaps the 0-48K segment with the segment between 64K-112K. This could be used for MP/M when running the 8085 processor.

<u>Option 2</u> swaps the 0-48K segment with the segment between 128K-176K. This could also be used with MP/M and the 8085.

<u>Option 3</u> swaps a 56K segment located between 4K-60K with a segment located between 68K-124K. This can be used to build an advanced disk operating system for CP/M-85.

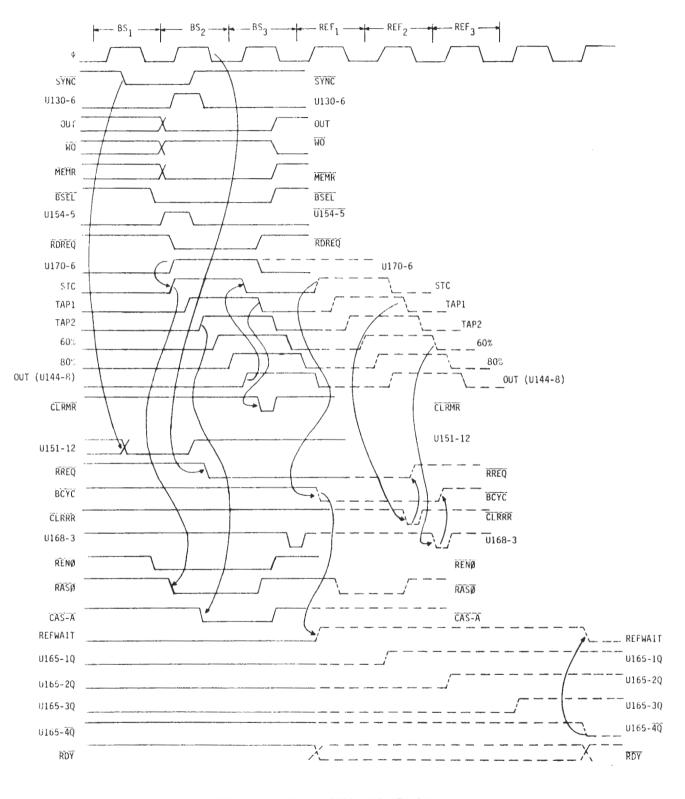

### REFRESH AND ARBITRATION LOGIC

The refresh circuits keep the dynamic RAM from losing its contents when the CPU isn't accessing a specific location. When the refresh circuits have control of memory, it disables the address multiplexer and enables the refresh address generator. The refresh address generator, a binary counter, places an 8-bit refresh address onto MAO-MA7.

At the same time, the refresh circuits send a control signal to the bank select circuit that forces it to enable all three memory banks. Subsequently, the same relative memory address is refreshed in each bank. When finished, the refresh circuits disable the refresh generator, increment its address count, and restore the address multiplexer and bank select circuits to normal operation.

The arbitration circuits determine if the refresh circuits or the CPU is to have control of the dynamic memory circuits. If the CPU is accessing memory when the refresh circuits attempt to refresh the RAM, the arbitration circuits will halt the refresh operation until the CPU is done.

Likewise, if the CPU attempts to access memory during the middle of a refresh operation, the arbitration circuits will stop CPU operation until refresh is completed. It does this by placing a logic zero on the S-100 RDY line. This line couples back to the active CPU to place the CPU into a wait state. While in a wait state, all of the CPUs register and signal lines do not change states; thus maintaining the processor's last valid status.

When the refresh circuit is finished refreshing the RAM, it brings the RDY to logic one. The CPU continues where it left off.

### PARITY CIRCUITS

The parity circuits monitor the number of bits written into each byte of memory. If the number of bits are odd, the parity circuits adds a logic one to the count and stores it in parity RAM. Otherwise, it stores a logic zero in parity RAM. Parity RAM consists of a  $64K \times 1-bit$  RAM IC for each  $64K \times 8$  memory bank.

When the CPU reads a memory location, the parity circuits count the number of bits in the 8-bit RAM location and adds it to the bit in the equivalent location in parity RAM. If the result is still even, everything is okay. However, if the total number of bits are odd, due to a bad memory chip for example, the parity circuits will assert the S-100 ERROR\* line.

In turn, the ERROR\* signal will send an interrupt request to the CPU. It is up to the user's program to process the interrupt.

The parity control line, from the memory control latch, allows you to disable the parity circuits, or to force a parity error for test purposes. In addition, a control line from the refresh circuits ensures that a parity error isn't generated during a memory write or a refresh.

2-58

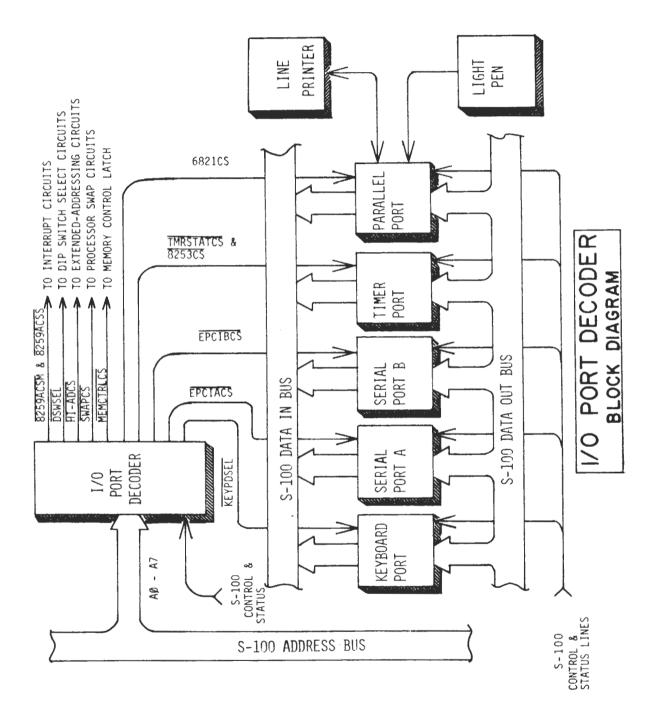

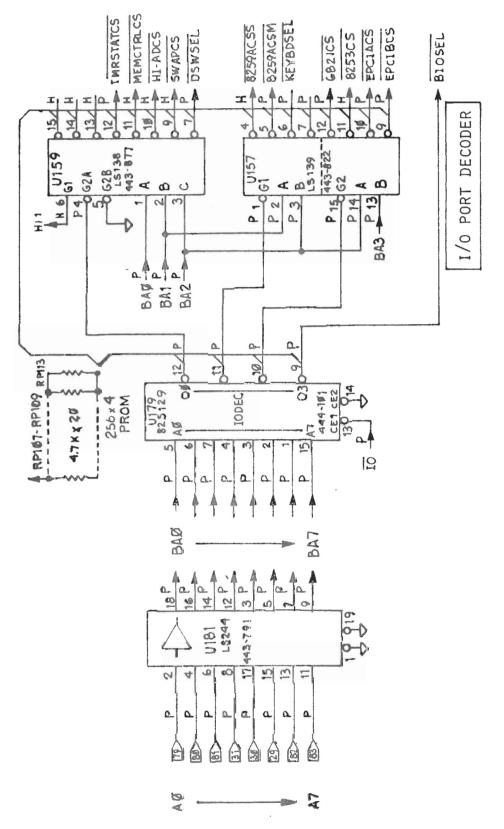

### I/O PORT DECODER

### GENERAL

The I/O port decoder provides enable lines to the data and control ports on the H/Z-100 motherboard. Each enable line is asserted by placing an address on AO-A7 of the address bus and asserting the appropriate S-100 control and status lines. The I/O port decoder responds by asserting the correct enable line.

The following lines have been discussed previously: 8259ACSM & 8259ACSS, DSWSEL, HI-ADCS, SWAPCS, and MEMCTRLCS. Refer to the appropriate block diagram description to see how these work.

The remaining lines control data transfer ports. This is done in conjunction with control and status signal from the S-100 bus.

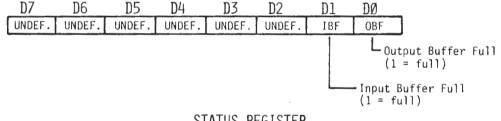

### KEYBOARD

The keyboard port contains an 8041A UPI, a dedicated microprocessor that handles all keyboard processing. When a key is pressed, the UPI determines which key it was, and sends the appropriate ASCII code to the computer. The UPI can also send an interrupt to the computer to tell it that it has a character ready. The program must provide the software to process this interrupt.

Through program control, you can change the ASCII code to a special code that sends out one byte pattern when the key is pressed, and another byte pattern when the key is released. This permits real-time applications. Other programming options include disabling the key-click, disabling the beep, and clearing the UPI's buffer.

To program the program processor, the CPU places the programming byte onto the S-100 data out bus and asserts KEYBDSEL. The appropriate S-100 control and status lines write the programming data into the keyboard circuits.

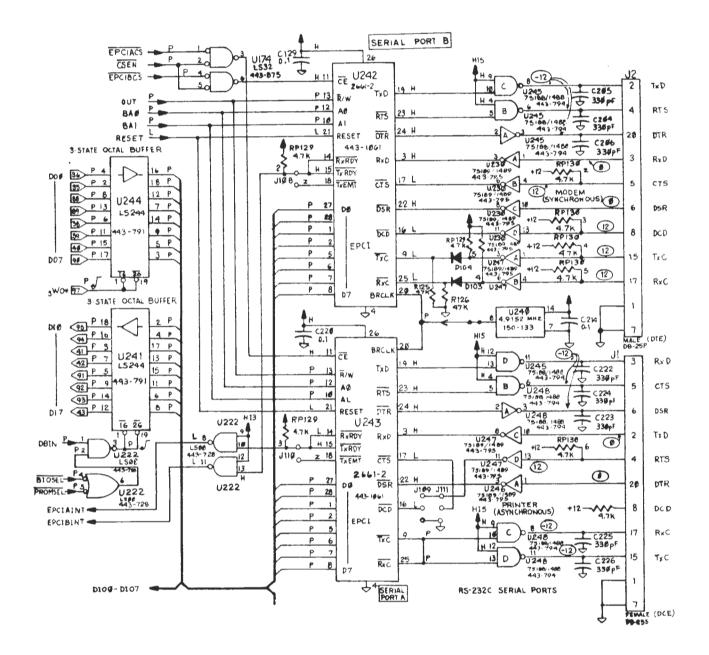

### SERIAL PORTS A AND B

Serial ports A and B provide RS-232 communications between the computer and the outside world. These ports feature programmable baud rate, synchronous or asynchronous operation, optional parity testing, and character transmission length.

Serial port A uses a DCE connector and can be used for an asynchronous device such as a printer.

Serial port B uses a DTE connector to connect to external devices. This port can be used for synchronous devices such as a MODEM.

Both ports can be polled or interrupt-driven. In a polled operation, for example, the CPU constantly checks the port's status register to see if it has received a data byte. If interrupt-driven, the CPU can be performing other tasks until the port has a character ready for transfer. When it does, the port sends an interrupt request to the CPU. If programmed to do so, the CPU finishes its current instruction and responds to the interrupt request.

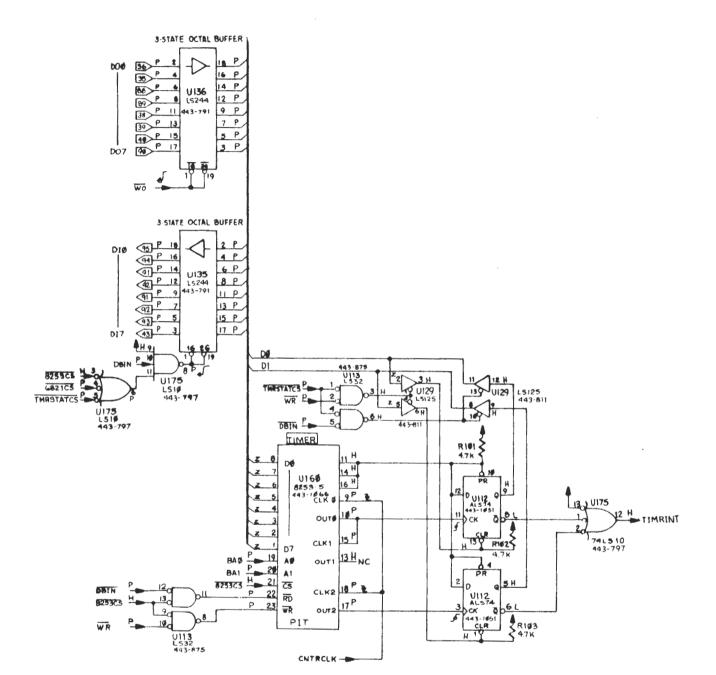

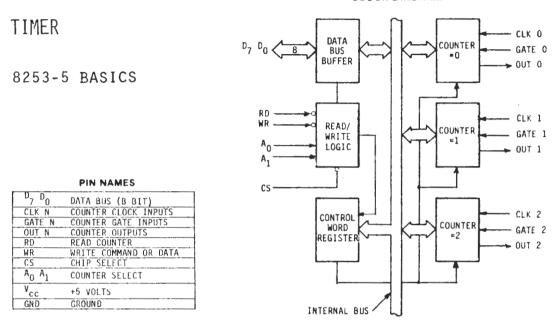

### TIMER PORT

The timer port contains an 8-bit counter and a 16-bit counter. These are driven by a 250-kHz crystal-controlled clock that is independent of the system clock. The timer circuits allow the CPU to perform other tasks, instead of spending time counting through a loop.

The CPU can load a starting count through the S-100 data out bus and, through software control, check the count through the S-100 data in bus. One application would be to translate the count into time-of-day or the date.

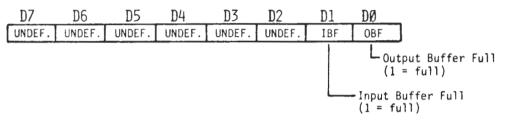

The timer will also generate an interrupt when it counts down from the preloaded number to zero. The CPU can use this for real-time applications such as displaying the total time on line, at one-second intervals, when running a MODEM program. PARALLEL PORT

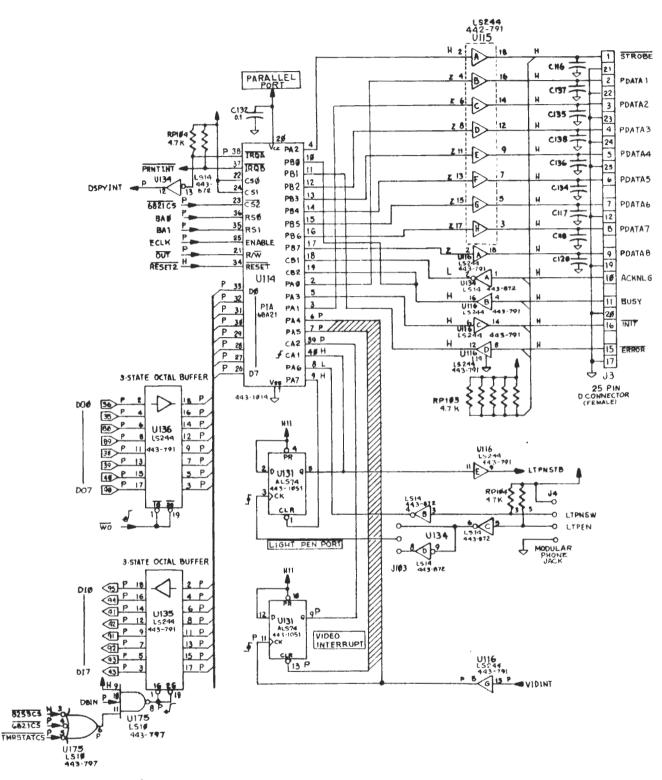

The parallel port processes two major I/O circuits: a line printer port and a light pen port. Not shown is an interrupt line from the video board.

The line printer port provides 8-bit parallel data output plus full handshaking. This port allows interfacing to some of the more popular line printers without having to buy a serial-to-parallel converter.

The light pen port permits using a light pen with the H/Z-100. When the light pen is placed near the CRT and detects a pixel, it strobes the CPU and the video board. Circuits on the video board store the location of the detected pixel. The user must supply the software to process this information (such as moving the pixel or drawing a picture).

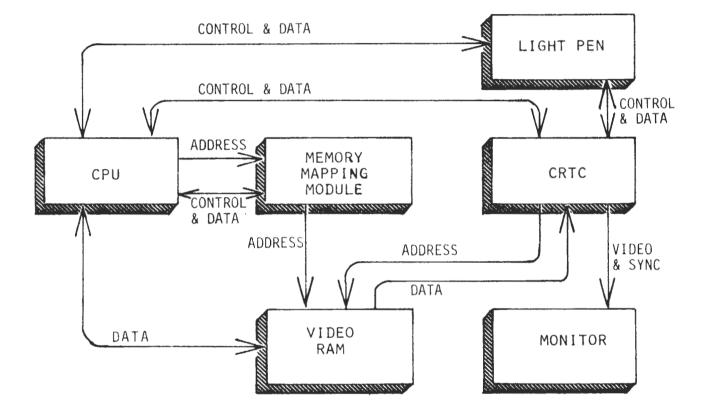

# BASIC VIDEO CIRCUITS BLOCK DIAGRAM

### BASIC VIDEO CIRCUITS

The CPU can access the video circuits as either a port or as a memory location. The CPU accesses the video circuits as a port to program the CRTC, and as a memory location to set up the character font or perform high-density graphics.

The CPU sends programming information to the CRTC along the control and data signal path. This information includes the number of characters and lines to be displayed, the scan rate, and cursor location.

Once programmed, the CRTC sequentially addresses the video RAM to fetch a character, convert it to serial, and send it to the monitor. The address counter increments, fetches the next character data, and the cycle repeats.

To write or read video memory, the CPU first programs the memory mapping module through the address and the control & data lines. The mapping module is necessary because the CRTC sees the VRAM address starting at zero and going to 64K, while the CPU sees the VRAM address starting at 744K and going to 936K. Once the mapping module is set up, the CPU can, for example, write a byte to 744K and the mapping module will send it to the same location that the CRTC sees as address 0.

The light pen circuits consist of the interface circuits discussed earlier and some counters on the video board. These registers hold the exact location of the pixel pointed to by the light pen.

Because of the complexity of the video board, we will discuss it in more detail.

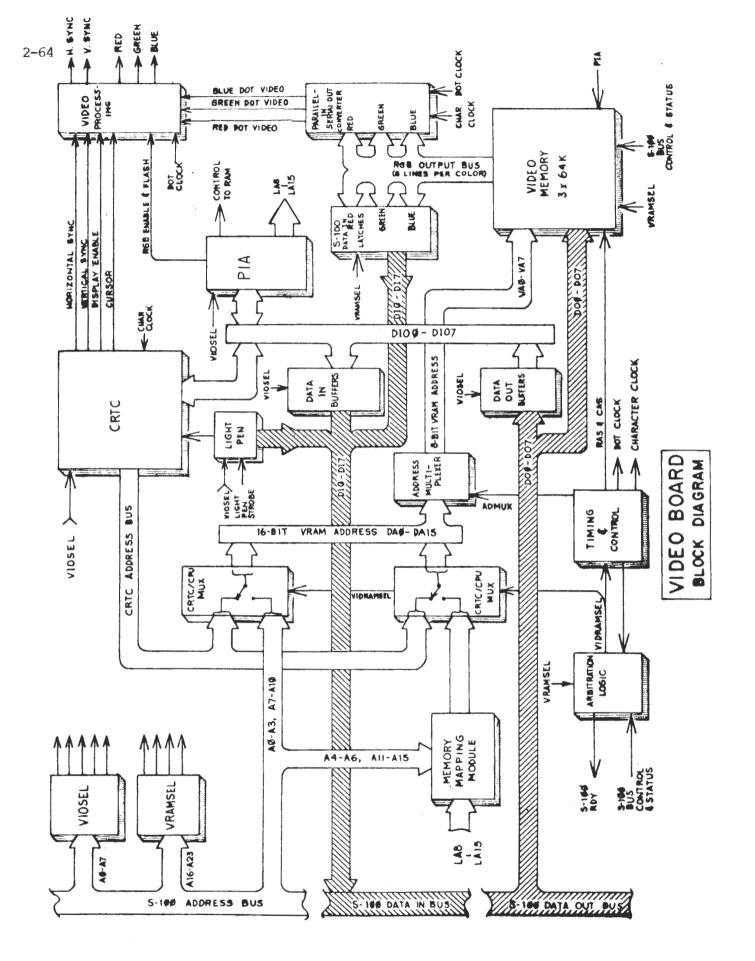

### VIDEO BOARD

### PROGRAMMING THE CRTC

The CPU programs the CRTC by asserting the appropriate VIOSEL line. VIOSEL is a port decoder that selects the right video port by monitoring address lines A0-A7. Programming data couples through the S-100 data out bus, the data out buffers, bus DIOO-DIO7, to the CRTC.

Similarly, the CPU can read certain CRTC registers through the S-100 data in bus and the data in buffers.

#### CRTC OPERATION

Once programmed, the CRTC sends the video RAM address to the CRTC/CPU address multiplexers. These multiplexers are normally in the address shown; that is, they couple the CRTC address to the 16-bit VRAM address bus, DAO-DA15.

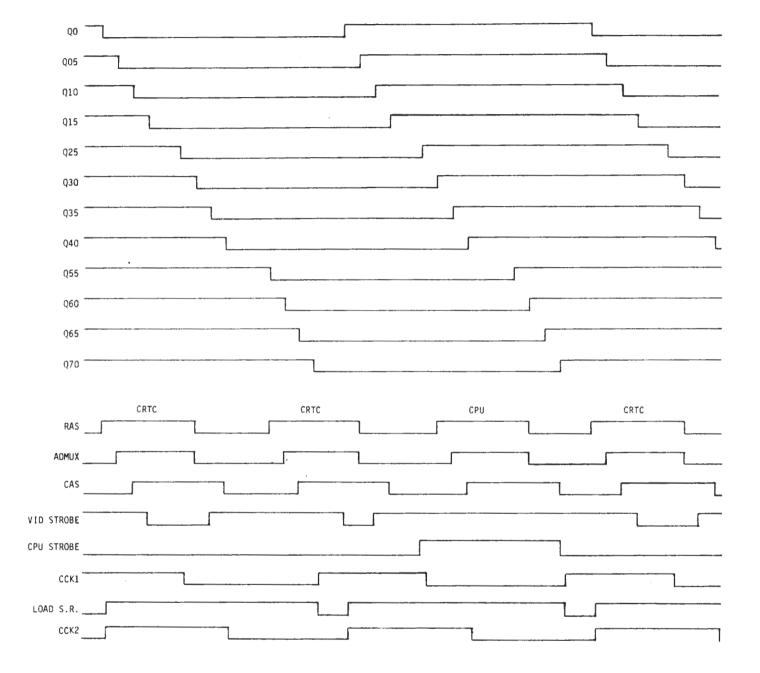

The 16-bit VRAM address bus connects the CRTC address to the address multiplexer. This circuit, under control of the ADMUX line, places the address onto the VRAM address bus, VAO-VA7, 8 bits at a time. At the same time, the timing & control block sends a RAS and CAS signal to the video memory to load each half of the 16-bit address into the row and column latches.

The video RAM is made up of three 32K x 8 banks located 64K apart. These banks can be expanded to 64K; however, this isn't supported at this time. There is one bank for each primary color; red, green, and blue. The minimum configuration for monochrome only has memory in the green bank. Otherwise, all three banks are filled.

The CRTC can only read video RAM, and it addresses all three banks at once. When the address lines are stable, the byte(s) are placed on the RGB output bus. There are 8 bus lines for each color.

The RGB buses connect to the CPU data-in latches, which are disabled, and to the parallel-to-serial converters. This circuit loads the parallel data in at the character clock rate and serially shifts it out at the dot clock rate (dot clock = 8 x character clock). The three serial dot video lines enter the video processing circuits.

At the same time the CRTC is addressing memory, it is also generating horizontal and vertical sync, blanking, and cursor information. These signals are also coupled to the video processing circuits where they are retimed to match the dot video data.

From here, these signals go through buffers to an RGB color monitor for display. Also, there are circuits to combine these pulses into a composite signal for output to a monochrome monitor.

A set of control lines also go to the video processing circuits. These are the RGB enable and flash lines. The RGB enable lines allow selectively turning off a particular color, while the flash line forces the screen to become a solid color. The exact color depends on what primary colors are enabled by the RGB enable line.

These enable lines are controlled by the PIA. In turn, the PIA is controlled by the CPU in the same manner that the CPU programs the CRTC. That is, one of the VIOSEL lines selects the PIA and the CPU reads or writes data through the DIOO-DIO7 bus.

### ACCESSING THE VRAM WITH THE CPU

When the CPU reads or writes video RAM, it asserts the lines from the VRAMSEL block. This block activates the appropriate gates and enables the desired color bank in memory. VRAMSEL does this by monitoring address lines A16-A23, which ensures that the address will always be an even 64-kilobyte boundary between 744K and 936K.

The CPU first programs lines LA8-LA15 of the PIA for a specific mapping pattern. The mapping pattern is fed to the memory mapping module where it is compared to address lines A4-A6 and A11-A15. The memory mapping module connects to one of the CRTC/CPU multiplexers. Address lines A0-A3 and A7-A10 connect directly to the other multiplexer.

When the CPU attempts to read or write memory, one of the VRAMSEL lines sends a request to the arbitration logic. The CRTC has top priority, so if the CRTC is accessing memory, the arbitration logic puts the CPU into a wait state by bringing S-100 RDY low.

When the CRTC is done, the arbitration logic activates VIDRAMSEL to switch the CRTC/CPU multiplexers to the CPU position. The mapped address couples through the address multiplexer to the RAM in the same manner as described for the CRTC.

If the CPU is writing data, it couples the data through DOO-DO7 to the memory circuits. It selects the correct bank with VRAMSEL. If reading data, the addressed byte(s) are placed on the RGB output bus and the CPU selects one of the three groups of CPU latches. The VRAM data couples to DIO-DI7 of the S-100 data in bus.

TIMING AND CONTROL

The ADMUX, RAS, and CAS timing was previously explained. The timing and control circuits also provide dot clock and character clock timing. The dot clock, at 14.112 MHz, is the basic timing frequency for the video board.

The timing circuits also provide a control signal to the arbitration logic. The video circuits are designed to let the CRTC have control of the video board for two RAS cycles, and let the CPU have control for the third cycle. The line from the timing block to the arbitration block tells the arbitration block when it can give the CPU control of the video circuits.

If the CPU isn't requesting control at this time, then nothing happens until the next RAS cycle, at which time the CRTC again has control of the board.

If the CPU is requesting control of the video board, indicated by VRAMSEL and signals on the S-100 bus control and status lines, the CPU will get control of the video board as described previously.

## DISASSEMBLY

- --- ---- - ----

|                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                | Cabinet Top Removal 22<br>CRT/Disk Drive Removal 22<br>Bottom Cover Removal 22<br>Keyboard Removal 22<br>Video Board Removal 22<br>Power Supply Removal 22<br>Motherboard Removal 22<br>LOW-PROFILE COMPUTER 22<br>Cabinet Top Removal 22<br>Disk Drive Assembly/Bottom Cover Removal 22<br>Keyboard Removal 22<br>Video Board Removal 22<br>Power Supply Removal 22<br>Power Supply Removal 22 | 2-71<br>2-72<br>2-74<br>2-74<br>2-75<br>2-76<br>2-77<br>2-78<br>2-78<br>2-78<br>2-78<br>2-78<br>2-80<br>2-81<br>2-82 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                      |

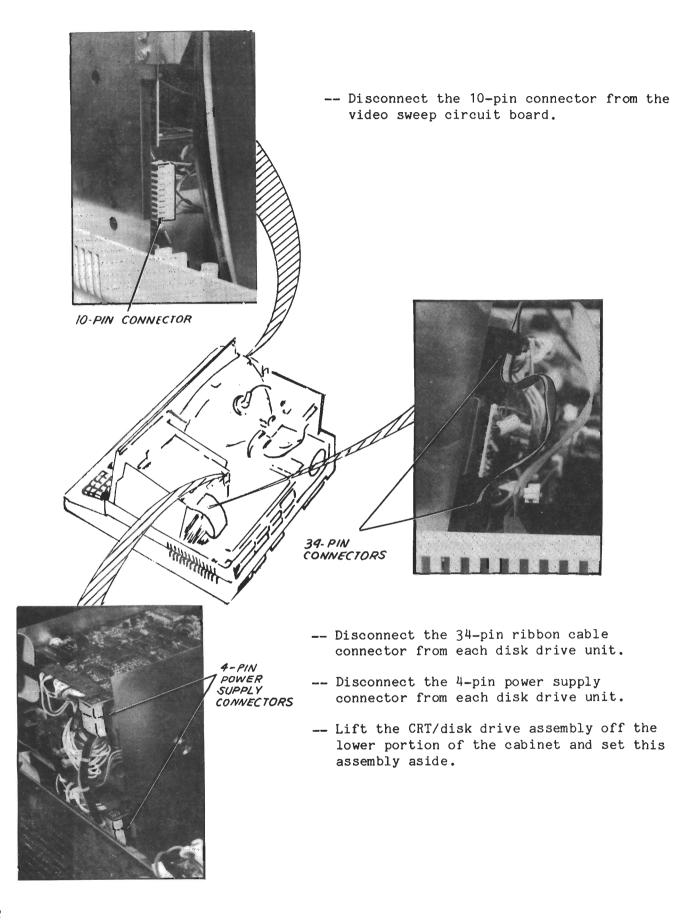

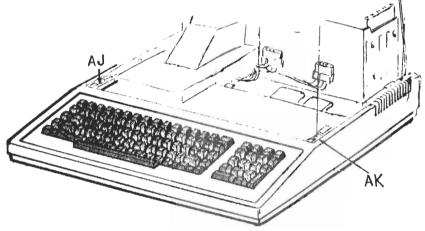

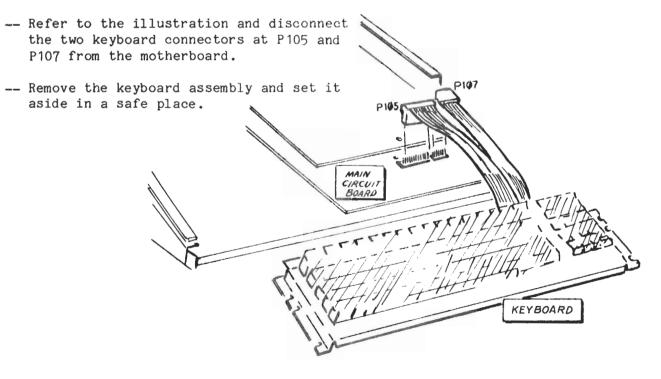

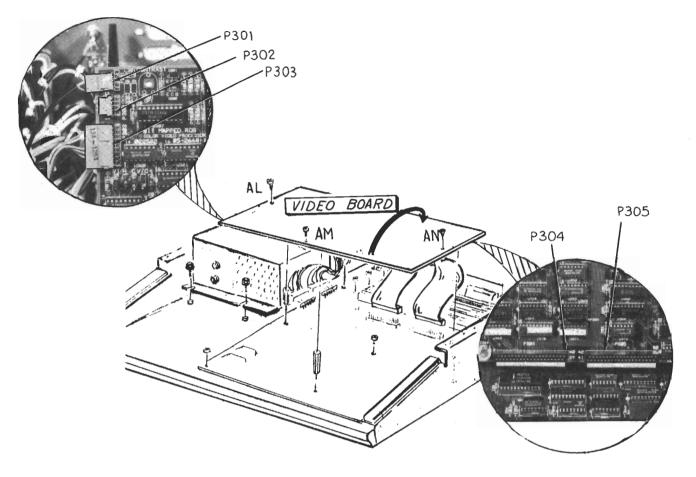

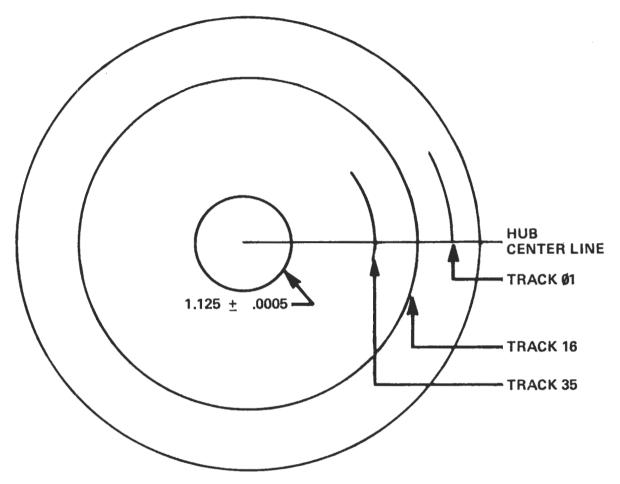

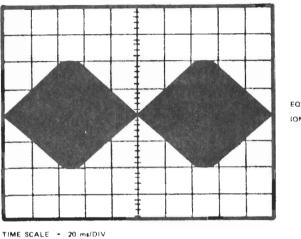

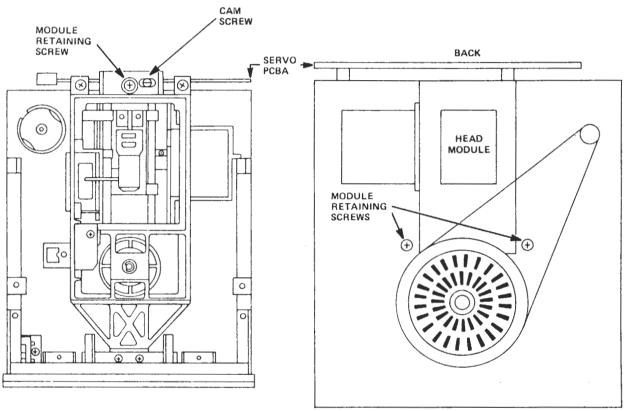

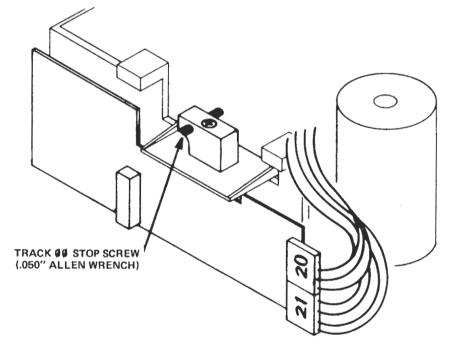

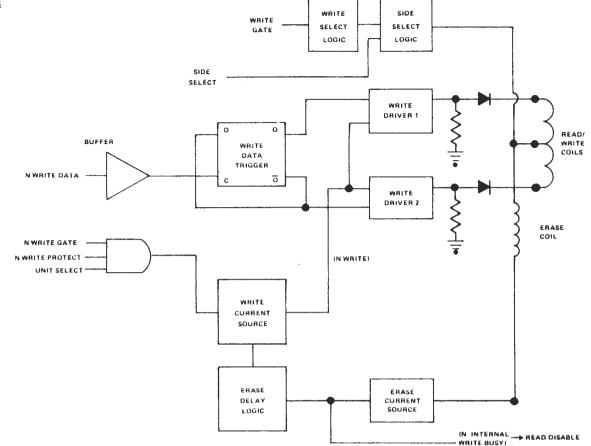

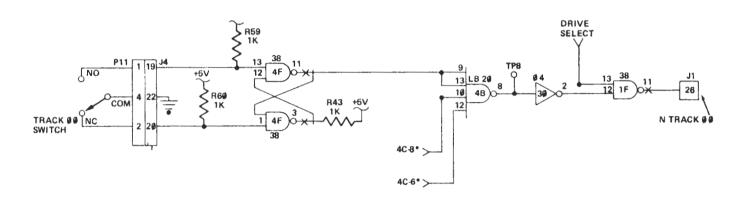

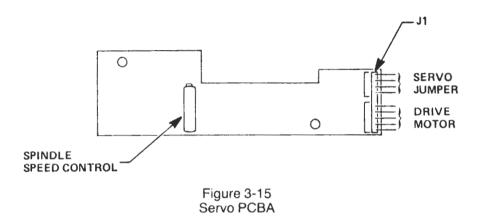

|                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                      |